# Transcending Static Deployment of Circuits: Dynamic Run-Time Systems and Mobile Hardware Processes for FPGAs

A THESIS SUBMITTED TO THE UNIVERSITY OF KENT AT CANTERBURY IN THE SUBJECT OF COMPUTER SCIENCE FOR THE DEGREE OF DOCTOR OF PHILOSOPHY.

> By Ralph Moseley September 2002

## Abstract

The usefulness of reconfigurable hardware has been shown in research and commercial applications. Unquestionably, this has and will lead to, unique avenues of thought within computer science being explored. The interest by researchers in some specific areas has led to manufacturers developing devices which were enhanced in their ability to dynamically be configured within a run-time context. These improvements are on-going and rapid progress is being made, producing high density, system-on-a-chip capable devices, with fast run-time reconfiguration.

The advancements in this technology have particularly led to a convergence between software and hardware domains, in the sense that algorithms can be implemented in either; the choice being dependent only in terms of efficiency within the medium itself. Older methods for development with these devices have become rapidly dated and inflexible. Very few suitable tools exist, for example, which are capable of fully utilising the inherent capabilities of such hardware.

The approach taken here allows the division between hardware and software to be diminished. Component designs, which may be hardware description language (HDL) based or synthesised algorithms, become easily manipulated and interacted with through a run-time engine, that can deploy elements at will to local or distributed devices. Such entities are essentially hybrid in nature, possessing both hardware and software functionality. These processes are sufficiently self-supporting, to be capable of being used outside of the run-time system within a normal Java development environment.

This work explores how hardware entities can become as dynamic as memory based algorithms within conventional von Neumann based systems, providing the means for extending the software programming paradigm into such areas. It analyses the possibilities of applying object-oriented and occam/Communicating Sequential Processes (CSP) based concurrency philosophies to these highly mobile, hardware processes.

## Contents

| Abstract                                                | iii                                    |

|---------------------------------------------------------|----------------------------------------|

| List of Tables                                          | viii                                   |

| List of Figures                                         | ix                                     |

| Trademarks                                              | viii viii viii viii viii viii viii vii |

| Acknowledgements                                        |                                        |

| 1. Introduction                                         | 1                                      |

| 1.1 Hardware Description Languages                      | 3                                      |

| 1.1.1 Introduction                                      | 3                                      |

| 1.1.2 History                                           | 3                                      |

| 1.1.3 Design Methodology                                | 5                                      |

| 1.1.4 Simulation                                        | 5                                      |

| 1.1.5 Register Transfer Level Synthesis                 | 7                                      |

| 1.1.6 HDL Support for synthesis                         | 8                                      |

| 1.2 Reconfigurable Systems                              | 8                                      |

| 1.2.1 Introduction                                      | 8                                      |

| 1.2.2 History                                           | 8                                      |

| 1.2.3 FPGA Architecture                                 | 9                                      |

| 1.2.4 Comparison to Alternatives                        |                                        |

| 1.2.5 Utilising Extra Capabilities                      |                                        |

| 1.2.6 Programming Reconfigurable ICs                    | 14                                     |

| 1.2.7 Reconfigurability                                 | 17                                     |

| 1.2.8 Partial and Dynamic Reconfiguration               | 17                                     |

| 1.2.9 Alternatives to Conventional Systems Architecture | 19                                     |

| 1.2.10 Software Design Tools                            | 20                                     |

| 1.2.11 Co-Synthesis                                     | 20                                     |

| 1.2.12 Convergence                                      |                                        |

| 1. 3 Current Research and Development in Reconfigurable Systems | 22  |

|-----------------------------------------------------------------|-----|

| 1.3.1 Main areas                                                | 22  |

| 1.3.2 Defining the problem tackled here                         | 23  |

| 2. Context                                                      | 25  |

| 2.1 Background                                                  | 25  |

| 2.1.1 Taxonomy and Defining the Area                            | 26  |

| 2.1.2 Logic Caching                                             |     |

| 2.1.3 Early Prototyping                                         |     |

| 2.1.4 Languages – Java                                          |     |

| 2.1.5 Visualisation and Manipulation with FPGA Tools            | 51  |

| 2.1.6 Further Development of Tools                              | 57  |

| 2.1.7 Sequencing the Hardware                                   | 62  |

| 2.1.8 A Dynamic Run-Time System                                 | 72  |

| 2.1.9 Analysis                                                  | 89  |

| 3. Design of a Solution                                         | 93  |

| 3.1 Philosophy of the Approach                                  | 93  |

| 3.1.1 Entities                                                  | 94  |

| 3.1.2 Capture                                                   | 98  |

| 3.1.3 Run-time                                                  | 99  |

| 3.1.4 Extrinsic Mobility                                        | 102 |

| 3.2 Language                                                    | 108 |

| 4. Implementation                                               | 116 |

| 4.1 Implementation Preface                                      | 116 |

| 4.1.1 Scope                                                     | 116 |

| 4.1.1 Hardware                                                  | 116 |

| 4.1.2 Design Tools                                              | 118 |

| 4.1.3 JBits                                                     | 122 |

| 4.2 System Implementation                                       | 141 |

| 4.2.1 System Overview                                                                                                                     | 141                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.2.2 Capture                                                                                                                             | 143                                    |

| 4.2.3 Scanning                                                                                                                            | 144                                    |

| 4.2.4 Code Production                                                                                                                     | 146                                    |

| 4.2.5 Input/Output Connection Points                                                                                                      | 151                                    |

| 4.2.6 Recapture                                                                                                                           | 155                                    |

| 4.2.7 Design Engine/Supervisor                                                                                                            | 158                                    |

| 4.2.8 Communications                                                                                                                      |                                        |

| 4.3 Mobile Hardware Processes and Design Considerations                                                                                   | 163                                    |

| 4.3.1 Resource Mappings and layout                                                                                                        |                                        |

| 4.3.2 Block RAM (BRAM)                                                                                                                    | 164                                    |

| 4.3.3 Bi-Directional Wires                                                                                                                |                                        |

| 4.3.4 Tri-State Wires                                                                                                                     |                                        |

| 4.3.5 Mobility                                                                                                                            |                                        |

| 4.3.6 Re-Use                                                                                                                              |                                        |

| 4.3.7 Interaction                                                                                                                         | 166                                    |

| 4.3.8 Usage outside of Reconnetics                                                                                                        | 166                                    |

| 5. User-Orientated Perspective                                                                                                            | 168                                    |

| 5.1 Introduction                                                                                                                          | 168                                    |

| 5.1.1 Scenarios for using Reconnetics                                                                                                     |                                        |

| 5.1.2 Mobile Hardware Processes                                                                                                           | 169                                    |

| 5.2 Engineering the Processes                                                                                                             | 169                                    |

| 5.2.1 Designing Processes                                                                                                                 |                                        |

|                                                                                                                                           | 170                                    |

| 5.2.2 PROCIO connect points                                                                                                               |                                        |

| <ul><li>5.2.2 PROCIO connect points</li><li>5.3 System Usage</li></ul>                                                                    |                                        |

|                                                                                                                                           | 171                                    |

| 5.3 System Usage                                                                                                                          | <b>171</b><br>171                      |

| <ul><li>5.3 System Usage</li><li>5.3.1 Description of the Development Cycle</li></ul>                                                     | <b>171</b><br>171<br><b>173</b>        |

| <ul> <li>5.3 System Usage</li> <li>5.3.1 Description of the Development Cycle</li> <li>5.4 Design Control Programming Tutorial</li> </ul> | <b>171</b><br>171<br><b>173</b><br>173 |

| 5.4.4 Design Control Program Example           |     |

|------------------------------------------------|-----|

| 5.4.5 Other Features                           |     |

| 5.4.6 Mobile Processors: A More Complex Design |     |

| 5.4.7 Communicating Processes                  |     |

| 6. Results and Evaluation                      |     |

| 6.1 Summary                                    |     |

| 6.2 Performance                                |     |

| 6.3 Comparison and Evaluation                  | 200 |

| 7. Future Work                                 | 203 |

| 8. Conclusions                                 | 207 |

| Glossary                                       | 210 |

| Acronyms                                       | 216 |

| References                                     | 219 |

| Appendix                                       | 224 |

| Appendix I: Language Reference                 | 225 |

| Appendix II: Design Examples                   | 239 |

| Appendix III: Reconnetics Class Descriptions   | 242 |

| Appendix IV: System Requirements               | 245 |

| Appendix V: KCPSM Xilinx Processor Details     | 246 |

## List of Tables

| Table 1. Comparison of reconfigurable computing to conventional CPU | 13  |

|---------------------------------------------------------------------|-----|

| Table 2. Instruction modules                                        | 67  |

| Table 3. Hardware and software in comparison                        | 71  |

| Table 4. Performance of system in milliseconds                      | 198 |

# **List of Figures**

| Figure 1. Behavioural level of abstraction                                | 5   |

|---------------------------------------------------------------------------|-----|

| Figure 2. Black box model                                                 | 6   |

| Figure 3. VHDL to netlist process                                         | 7   |

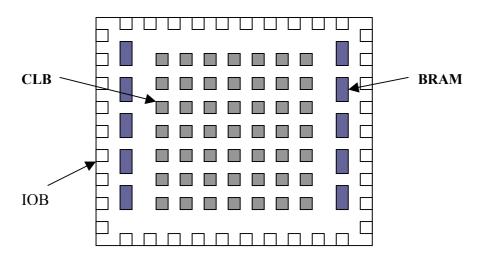

| Figure 4. Internal architecture of an FPGA                                |     |

| Figure 5. Virtex internal slice                                           | 11  |

| Figure 6. Comparison of generic and FPGA design                           | 14  |

| Figure 7. Classification of FPGAs according to configurability            |     |

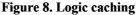

| Figure 8. Logic caching                                                   |     |

| Figure 9. Diagram of prototyping system                                   |     |

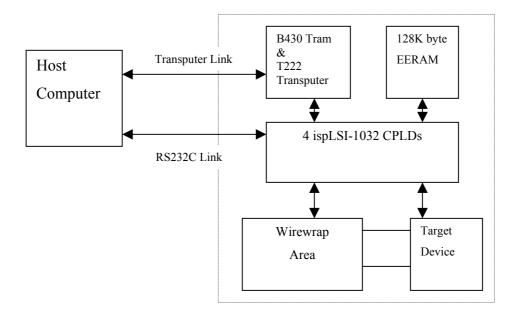

| Figure 10. Typical life-cycle of an entity                                |     |

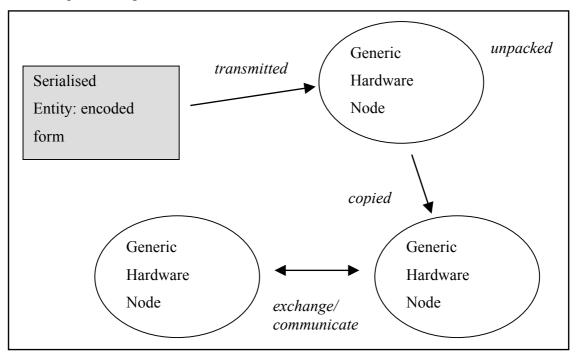

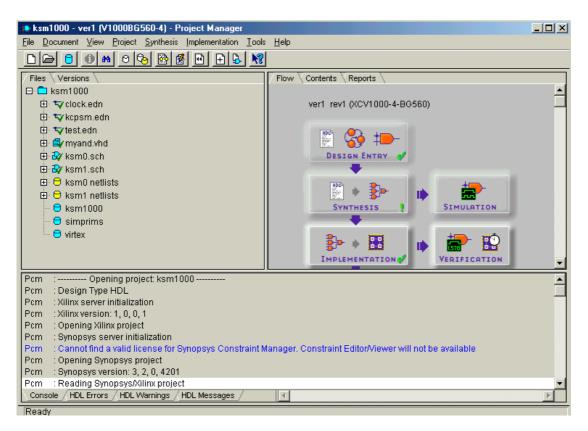

| Figure 11. The Schematic editor                                           | 117 |

| Figure 12. Foundation project manager                                     |     |

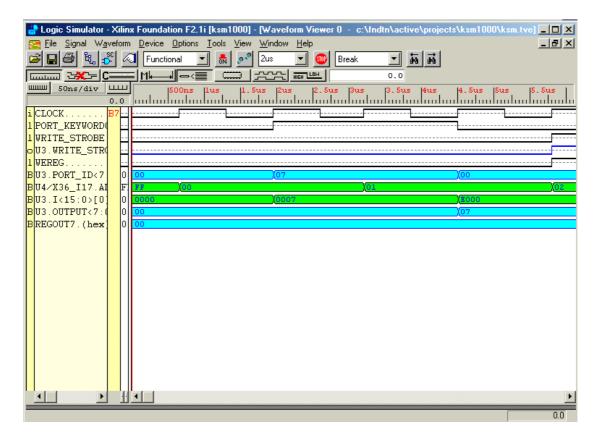

| Figure 13. The logic simulator                                            | 119 |

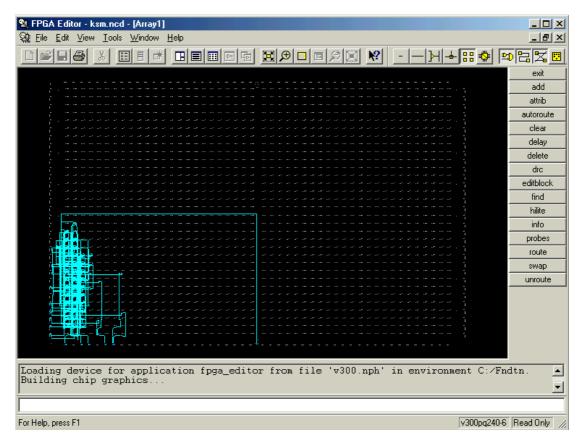

| Figure 14. FPGA Editor                                                    | 121 |

| Figure 15. Virtex device resource overview                                |     |

| Figure 16. Slice overview                                                 | 124 |

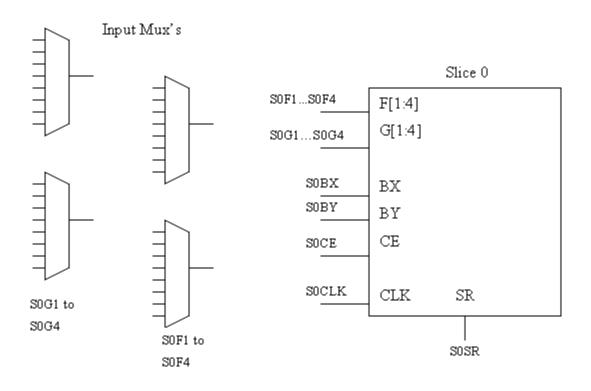

| Figure 17. Input multiplexors on slice 0                                  |     |

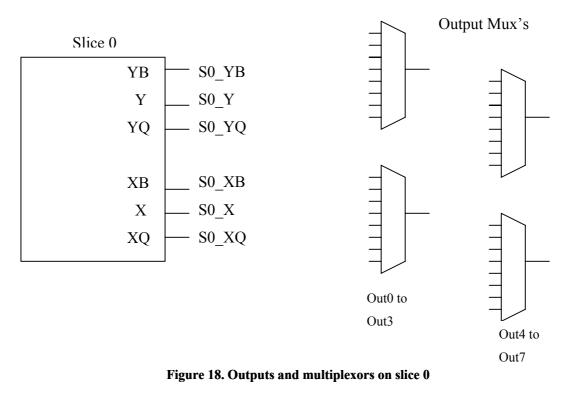

| Figure 18. Outputs and multiplexors on slice 0                            | 127 |

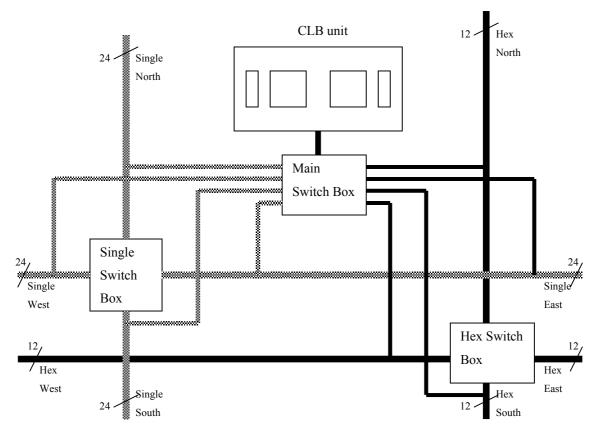

| Figure 19. Virtex routing overview                                        |     |

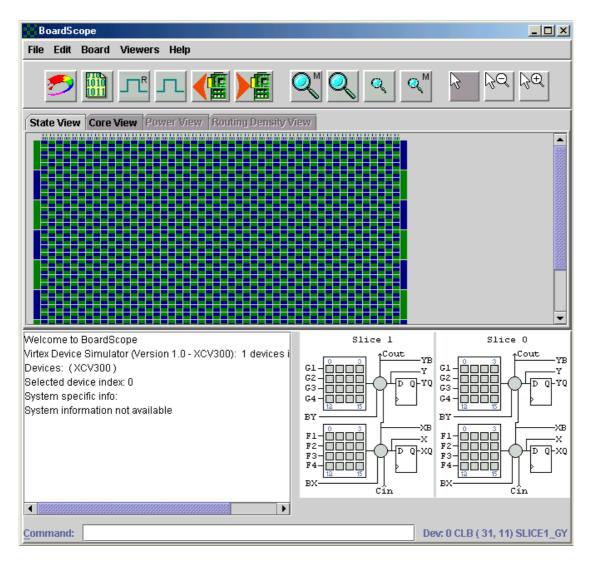

| Figure 20. Xilinx BoardScope application                                  |     |

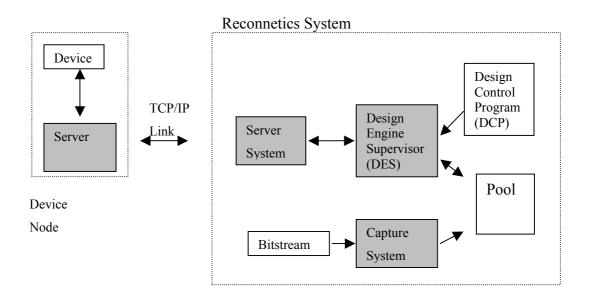

| Figure 21. Reconnetics overview                                           | 141 |

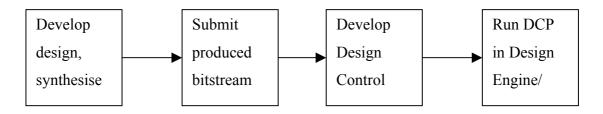

| Figure 22. Development cycle                                              | 142 |

| Figure 23. Capture system showing main classes                            | 143 |

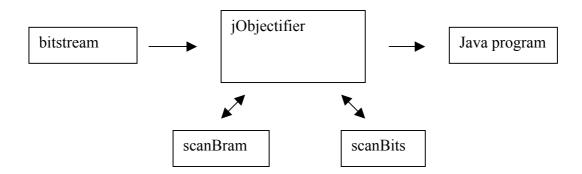

| Figure 24. Capture system                                                 | 146 |

| Figure 25. Pre-capture system showing main classes used                   | 151 |

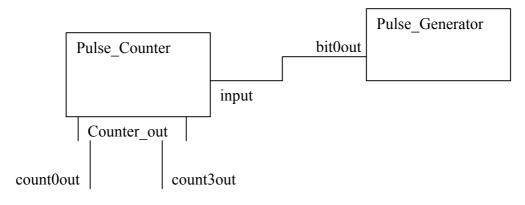

| Figure 26. PROCIO unit showing main connections                           | 152 |

| Figure 27. Process buffering (before) showing logical user view           | 153 |

| Figure 28. Process buffering (before) showing actual physical view        |     |

| Figure 29. Process buffering (after) showing I/O buffers in physical view | 153 |

| Figure 30. Recapture main classes                                         |     |

| Figure 31. Recapture system                                               |     |

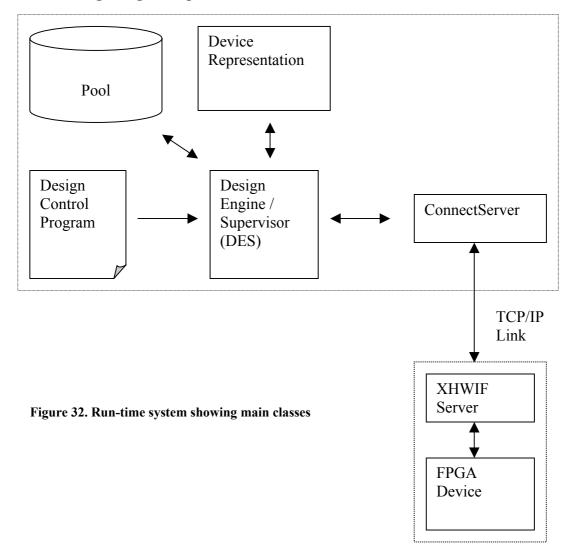

| Figure 32. Run-time system showing main classes        | 158 |

|--------------------------------------------------------|-----|

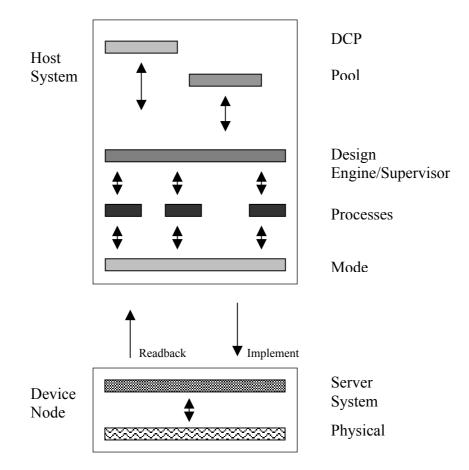

| Figure 33. Run-time visualisation                      | 160 |

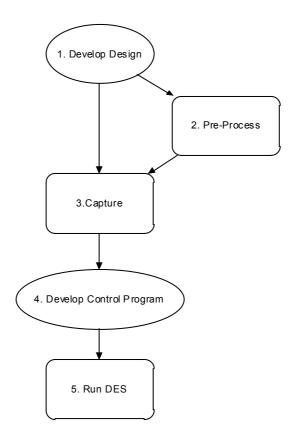

| Figure 34. Diagram showing design cycle                | 171 |

| Figure 35. Example visualisation                       |     |

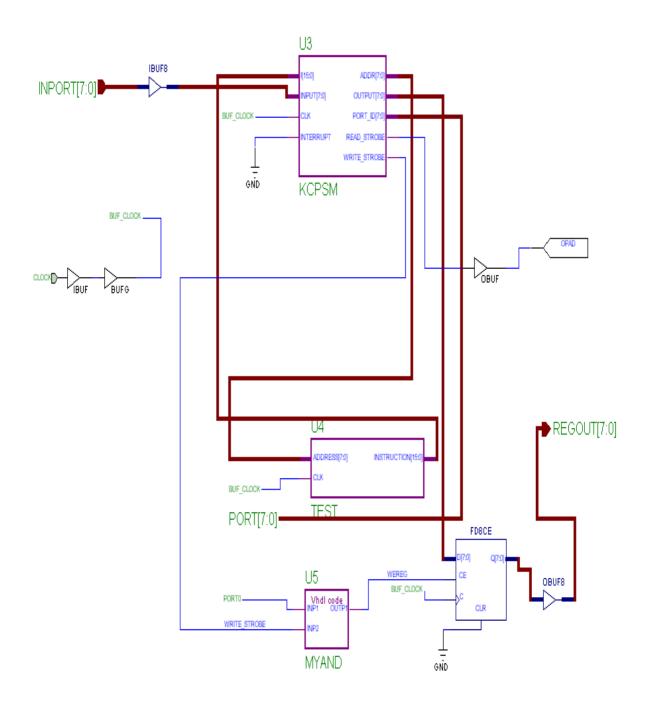

| Figure 36. Schematic for a simple microcontroller test |     |

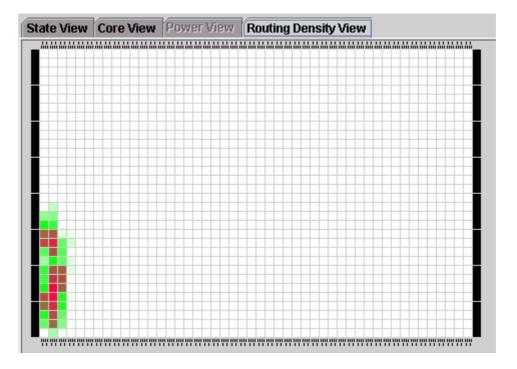

| Figure 37. BoardScope showing implement design         | 189 |

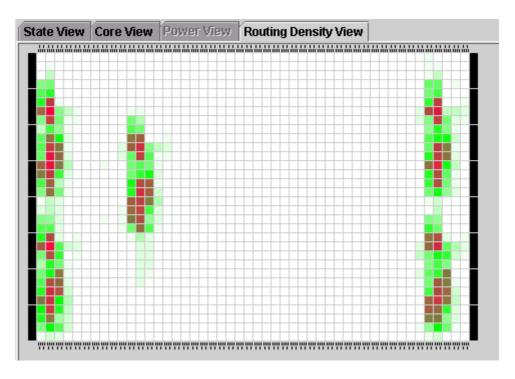

| Figure 38. BoardScope showing five processors          | 192 |

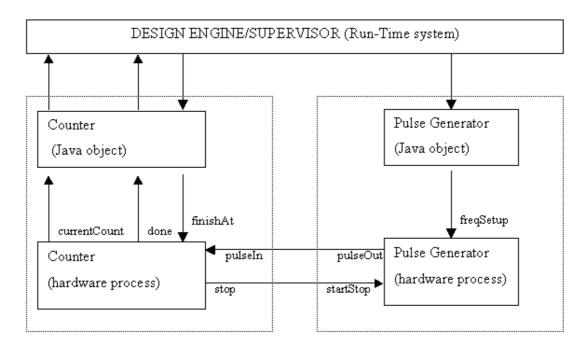

| Figure 39. Communicating processes                     | 193 |

## Trademarks

Java is a trademark of Sun Microsystems, Inc. in the United States and other countries.

Foundation, Virtex, Virtex E and JBits are trademarks of Xilinx, Inc.

Windows and Windows 2000 Professional are trademarks of Microsoft Inc.

Handel-C and DK-1 are trademarks of Celoxica Ltd.

Photoshop is a trademark of Adobe Systems Inc.

Lightfoot is a trademark of Digital Communication Technologies.

ABEL is a trademark of Data I/O Corporation.

## Acknowledgements

Thanks to Xilinx for producing the Virtex hardware and most of all to the JBits team who have been very helpful in my endeavours. Thanks also to my supervisor, David Wood and the University of Kent at Canterbury Computing Laboratory, for supporting this project.

The versatility of field programmable gate array (FPGA) technology has led to its widespread use in consumer goods and appliances, as well as industry. Its use spans from communications equipment and computer cards, through to space and military applications. Research utilising FPGAs has flourished in many avenues, ranging from evolutionary computing [44], fault tolerant systems, to internet reconfigurability.

FPGAs have greatly improved over past years. This has been in both capacity and functionality. Capacity, for example, now stands at around 10 million gates, with additional block RAM also included. Internal clocks within such devices can now be as high as 500 MHz.

One of the main features of FPGA technology, its ability to be totally reconfigured over its life cycle many times, has also improved. Certain FPGAs can be reconfigured dynamically, that is, areas of the device can be changed while currently running, without disturbing any adjacent circuitry.

Hardware engineering design previously was a static venture, concerned with building in module form, prior to a single download. This modular format could take in many different approaches, from graphical tools, through to languages such as VHDL and Verilog. More recently, behavioural languages have become present, such as Handel-C. All these methods of development can be used singularly or together, forming one design which is synthesised and finally compiled down to a single bitstream<sup>1</sup> for download to FPGA.

Software engineering paradigms are being applied to hardware design in this area. Behavioural languages, as mentioned above, relate more to a software development cycle and the actual language itself is aimed at a software engineer's viewpoint and experience. There is a convergence of fields, both at design and run-time.

The reconfigurability of the FPGA and the ubiquity of the internet, has led to devices being able to be reprogrammed, while deployed in the field. A piece of hardware can thus be updated to the latest specifications or changes made while the customer is actually still using the equipment. Yet another use is the remote configuration of equipment which cannot be reached by a human engineer, in hostile or far off locations, such as deep space or in orbiting satellites. For extreme environments, hardened versions of FPGAs exist, resilient to electromagnetic radiation, which may corrupt configuration data.

There is a slow progression to a much more dynamic approach to hardware development, which captures much of what has been learnt in software engineering. FPGA technology allows ever greater expansion along this route, with its static based memory, which can be updated in real time – analogous to computer memory that can be accessed at any given point<sup>2</sup>.

The work related here focuses on improving the flexibility and manipulation of programming FPGAs at a high-level and introduces ideas concerning mobility of design components.

This thesis is divided into eight sections. Section 1 provides a broad introduction to the areas discussed and an overview of concepts, finally framing the problem untaken. Section 2 reviews previous work in this area, giving examples and the extent of other researcher's aspirations, ending with an analysis of the material. The third section

<sup>&</sup>lt;sup>1</sup> The name given to the single binary file which makes up a configurable image in a FPGA.

<sup>&</sup>lt;sup>2</sup> A few comprehensive surveys exist of reconfigurable technology [7, 10] and possible futures [25].

extends the analysis, providing an exploration and possible philosophy of approach towards a solution. Section 4 provides detail of the implementation, together with introductory material on less known areas. A user perspective of the system is offered in section 5, together with a tutorial and examples. In section 6 there is assessment and evaluation of the system, providing feedback on performance. Future possibilities are then drawn from this, including possible improvements. Finally, section 8 places the results in context with the initial goals for analysis and conclusion. Other material in the form of a glossary and appendices are added for support of the main work and the reader's understanding.

## **1.1 Hardware Description Languages**

This section serves as an introduction to the broad areas involved in this work, that is, the design process, particularly the use of languages and the reconfigurable hardware itself.

#### **1.1.1 Introduction**

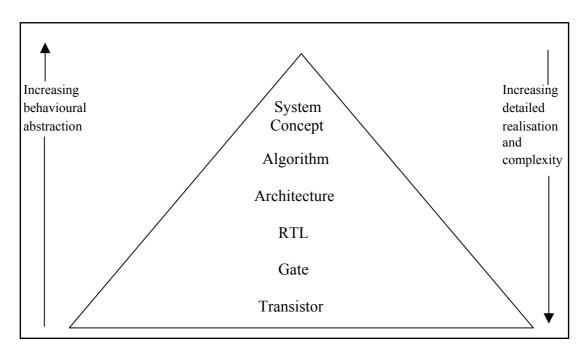

A HDL is a programming language used to model the intended operation of a piece of hardware. There are two aspects of the description of hardware that the language can facilitate; abstract behaviour and hardware structure modelling. Behaviour modelling provides a way of simulating hardware without necessarily being structurally descriptive. Hardware structure modelling represents an accurate model of the physical architecture. The behaviour of hardware may be visualised at various levels of abstraction. Higher level models describe the operation of hardware structure.

### 1.1.2 History

The US government was the main motive force behind the development of VHDL [3, 42]. In 1980 the decision was made to try and make circuit design self-documenting, following a common design methodology and be reusable with new technologies. There was a need for a standard programming language for describing the function and structure of digital circuits for the design of integrated circuits (IC's). The US Department of Defence (DoD) funded a project under the Very High Speed Integrated

Circuit (VHSIC) program to create a standard HDL. The result was VHSIC hardware description language or VHDL. It was ratified by the Institute of Electrical and Electronic Engineers (IEEE) in 1987 as IEEE Standard 1076.

The F-22 advanced tactical fighter aircraft was the first major program to make use of VHDL descriptions for all electronic subsystems in the project. Different subcontractors designed various subsystems and so the interfaces between them were crucial and tightly coupled. The VHDL code was self-documenting and formed the basis of the top-down strategy.

Another popular HDL is Verilog, developed in 1983 by a Computer Aided Engineering (CAE) company called Gateway Design Automation. This has had some commercial success. For example, of all the designs submitted to ASIC foundries in 1993, 85% were designed and submitted using Verilog<sup>3</sup>. In December 1995 the Verilog language was reviewed and adopted by the IEEE as IEEE standard 1364.

There is very little difference, except perhaps stylistically, between the two languages. The choice of using either usually comes down to personal preference and the availability of tools to do a specific task – such as modelling, or simulating the chosen language.

Yet another HDL is ABEL (Advanced Boolean Equation Language)<sup>4</sup>, which was invented to allow designers to specify logic functions for realisation in programmable logic devices (PLD). ABEL is modular in form and is device independent, that is, the target could be any device. Originally, this would have been small scale PLDs but now larger devices can be programmed through other methods i.e. through fuse patterns.

More recently, behavioural languages based on concurrent versions of C have been introduced for design. The basic idea being to describe the functionality, rather than the structure of a circuit. This more closely resembles the software design process

<sup>&</sup>lt;sup>3</sup> Source EE Times.

<sup>&</sup>lt;sup>4</sup> ABEL is a trademark of Data I/O Corporation.

than hardware engineering, although usually it is necessary to include some structural references or physical properties within such code.

Software used to assist in the design of hardware come under one of two categories: Computer Aided Design (CAD) and Computer Aided Engineering (CAE). Tools used to design circuit board related hardware come under the category of CAD, while others used for chip design come under the category of CAE. However, the distinction is not that fine, as a simulator could be used to model both boards and ICs.

### 1.1.3 Design Methodology

The basis of electronic design is essentially top down [43]. Ideally this would mean describing a complete system at an abstract level, using a HDL and automated tools, for example, partitioners and synthesisers. This would create the design in implementation on PCBs or multi-chip modules (MCM) which contain standard ICs, ASICS, FPGA, PLDs and full-custom ICs. This dream has not been fulfilled totally but is rather the goal to which EDA tools strive.

Figure 1. Behavioural level of abstraction

#### 1.1.4 Simulation

Simulation is a fundamental and essential part of the design process for all kinds of electronic based products. For ASIC and FPGA devices, simulation is the process of

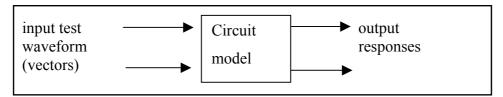

verifying the functional characteristics at any level of behaviour, that is, from highlevels of abstraction to low-levels [33]. The basic format of a simulation is:

Simulators use the timing defined in an HDL model before synthesis, or the timing from the cells of the target technology library after synthesis. A simulator can model only the basic behaviour of a circuit, or be a detailed dynamic timing analysis, or both. Static timing analysis is used during optimisation, extracting delays from the cells of the technology library but has several difficulties, such as multiple clocks, complex clocking schemes, asynchronous circuits, transparent latches and identifying and ignoring false paths.

There is a particular type of simulation known as fault simulation, which has particular input stimuli (vectors) and typical manufacturing faults injected into the model. The idea here is to:

- Identify areas of a circuit that are not being functionally tested by the functional test vectors.

- Check the quality of test vectors and their ability to detect potential manufacturing defects.

- To perform board and in-circuit chip testing for both production and repair testing.

This area has become particularly important for several reasons, such as the vast increase in the number of gates on a chip, the increased gate to pin ratio and the reduced timing of sub-micron transistor technology. Early fault simulation has, because of these factors, the ability to reduce costs considerably.

## **1.1.5 Register Transfer Level Synthesis**

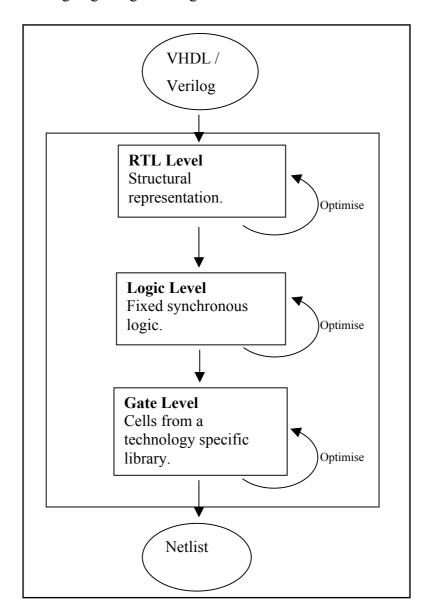

Register Transfer Level Synthesis is the process of translating a register transfer model of hardware, written in a HDL at the register transfer level, into an optimised technology-specific gate level implementation. A RTL synthesis tool automates this part of ASIC and FPGA design process. Synthesis is by far the quickest and most effective means of designing and generating circuits.

Figure 3. VHDL to netlist process

#### **1.1.6 HDL Support for synthesis**

Certain constructs in a HDL are either ignored or are not supported by synthesis tools. The reason here is that some constructs have no direct hardware correlation, or the hardware intent is extremely abstract. For example, timing related constructs are ignored, as the timing should come from the cells of the technology specific library. Constructs that are not supported typically include; floating point arithmetic operators, loop statements without a globally static range and file manipulation related constructs. What is and what is not supported varies between vendors, although a VHDL working group has been set up to formalise an industry standard subset of constructs that should be supported by synthesis tools, with the intention of making designs portable.

## **1.2 Reconfigurable Systems**

#### **1.2.1 Introduction**

The boundary that once existed between hardware and software has drawn rapidly smaller. This is not only true of our expectations in terms of execution speed but also the ability of what was once solid state physical circuitry to become mouldable to the requirements of the software and the problem domain itself. It would seem that the hardware is becoming as flexible and as expressive as the underlying software, determined only by the constraints of the description language and development tools.

These reconfigurable systems are based on programmable logic, such as the recent large capacity FPGAs, the newly available analogue equivalent – the Field Programmable Analogue Array (FPAA) and to a lesser extent, application specific integrated circuits (ASIC).

#### 1.2.2 History

These devices are capable of being programmed to perform any possible logic function. They actually evolved from the programmable logic array (PLA) devices of the early 1970s. The basic structure of the PLA was a matrix of AND, OR and inverter gates, together with a series of programmable switch arrays, which allowed connections to be formed through the chip. A simplified version was also produced,

called programmable array logic (PAL), which cut down on the number of gates needed to form functions, by introducing a form of feedback.

Both of these types of circuit were particularly good for combinational circuits (a circuit whose outputs only depend on its current inputs) but needed additional external flip-flops for use in sequential designs (a circuit with memory, whose outputs depend on the current input and the sequence of past inputs). In response to this need SPLDs (simple programmable logic device) were developed, which included the flip-flops and multiplexers for selection purposes. Each section including the logic gates, flipflops and multiplexers that drive each output became known as a macrocell. We see now the development into larger devices with sub-divided structures. Larger chips were developed which combined many SPLDs, these became known as CPLDs (complex programmable logic devices); an example of this type is the Xilinx XC9500 series. The XC95108 contains six configurable function blocks (CFBs) which is equivalent to an 18 macrocell SPLD with 36 inputs and 18 outputs. The outputs of the macrocells exit the I/O pins but also feed back into a global interconnection matrix. By using feedback signals, very complex multi-level logic functions can be built by programming the individual logic functions of the macrocells in each CFB and then connecting them through the switching matrix.

#### **1.2.3 FPGA Architecture**

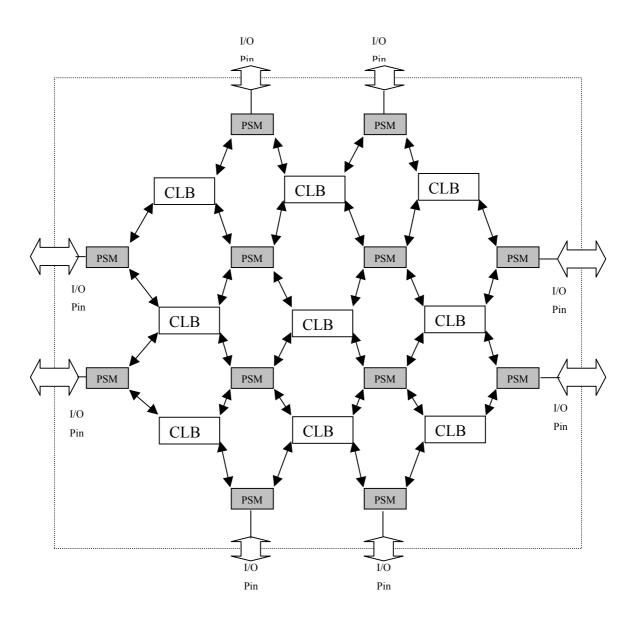

An alternative architecture is found in FPGAs [26, 47]. The basic building block here is the look-up table (LUT). A typical LUT consists of four inputs and a small memory of 16 bits. Applying a binary combination to the inputs will match the address of a particular memory bit and make it output its value. Any four-input logic function can be built by programming the look-up table with the appropriate bits. For example, a four-input AND gate is built by loading the entire memory with 0 bits, except for a 1 bit that is placed in the cell that is activated when all bits are 1. In the Xilinx XC4000 series there are three LUTs combined with two flip-flops and some additional steering circuitry, to form a configurable logic block (CLB). The CLBs are arranged in an array with programmable switch matrices (PSMs) between. The PSMs form a similar function to the switching matrix in the CPLD, in that they route outputs from neighbouring CLBs to the inputs of a CLB.

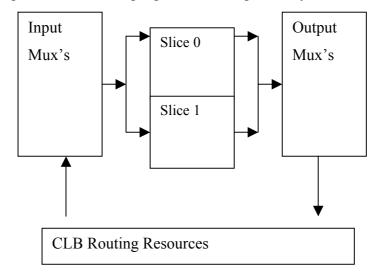

Figure 4. Internal architecture of an FPGA

The main question that arises for these devices is how these switches are set. Initially, in the case of early programmable devices, the switch arrays were manufactured with fuses at every cross point, such that every input was connected to each logic gate. Using special circuitry it was possible to burn out fuses at the cross-points to unwanted connections, eventually only leaving the desired logic functions. The disadvantage here was that once the fuses were blown, they could not be reset, so if there was a mistake, the entire device had to be thrown out and a new device programmed. In XC9500, XC4000 and Virtex families, the fuses are replaced with programmable switches. Each switch is controlled by a storage element that records its state. Changing the storage element's value changes the state of the switch and

alters the functions of the device. This can be done repeatedly to implement new designs, or alter faulty ones, eliminating the need to buy a new device for each design.

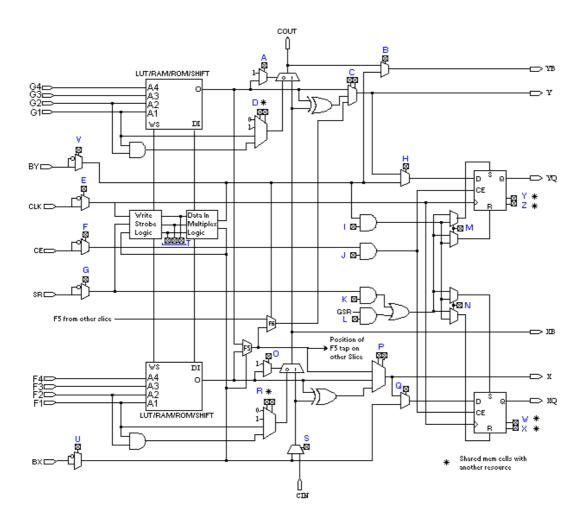

Figure 5. Virtex internal slice<sup>5</sup>

The XC9500 CPLDs use a non-volatile FLASH-based storage cell which retains its program even if there is no power. The XC4000 and Virtex families, along with most other common FPGAs, use random access memory (RAM), which needs to be reprogrammed each time the power is interrupted. This can either be done via download from a computer, or more likely, automatically at power up from an EPROM containing the design.

<sup>&</sup>lt;sup>5</sup> Schematic from JBits user documentation.

#### **1.2.4 Comparison to Alternatives**

ASIC devices are partially manufactured by a vendor in generic form. This initial manufacturing process is the most complex, time consuming and expensive part of the whole process. The result is silicon chips with an array of unconnected transistors. The final manufacturing process of connecting the transistors together is then completed when a chip designer has a specific design for implementation. A vendor can usually do this in a couple of weeks. FPGAs cannot compare to ASIC technology in terms of speed and density but provide much greater flexibility, cost and rapid turnover of designs. Hardware compilation into FPGAs enables realistic working hardware-software systems in hours or even minutes.

FPGAs are completely manufactured but remain design independent. The vendor manufactures devices to a proprietary architecture, however, this includes a number of programmable logic blocks that are connected to programmable switching matrices. To configure a device involves downloading netlists into the logic blocks and programming the switching matrices to route signals between selected areas. One of the main advantages to using FPGAs over ASIC devices is that a designer can do this himself without sending out the design. Also, the FPGA can be reprogrammed at any time.

#### 1.2.5 Utilising Extra Capabilities

While the current tools are capable of adequately programming and developing these reconfigurable systems, there exists much scope for both new design methods and dynamic functionality, which draws on the extra capabilities inherent in such flexible systems.

The advantages of reconfigurable systems are fairly obvious; they have use in emulating systems, developing easily alterable systems and quick development in rapid prototyping. It is possible, for example, to find the design libraries for most logic components, such as those within the 74 series. Cores are also available for most processors, such as the 68000 or 808X. These designs, once downloaded, act in exactly the same way as the original functionally and in some cases better, allowing faster clock rates to be achieved. Core designs can be found and downloaded – free – over the internet and there is a trend toward this.

| Algorithm    | FPGA     | Comparison     | Speedup |

|--------------|----------|----------------|---------|

|              | System   | СРИ            |         |

| DNA          | SPLASH 2 | SPARC 10       | 43000   |

| matching     |          |                |         |

| RSA Crypto   | PAM      | Alpha 150MHz   | 17.6    |

|              |          |                |         |

| Ray Casting  | RIPP-10  | Pentium 75 MHz | 33.8    |

|              |          |                |         |

| FIR Filter   | Xilinx   | DSP 50MHz      | 17.9    |

|              | FPGA     |                |         |

| Hidden       | Xilinx   | SPARC 10       | 24.4    |

| Markov Model | FPGA     |                |         |

| Spec92       | MIPS+RC  | MIPS           | 1.12    |

Table 1. Comparison of reconfigurable computing to conventional CPU<sup>6</sup>

FPGAs have contributed significantly in logic design by stimulating new areas of application. PLAs, PALs and other forms of programmable sequencers have mainly been used for traditional logic replacement, which may reduce overall chip count and board complexity. FPGAs can be seen as an alternative medium in which to compile algorithms, particularly for differing systems, not based on the von Neumann architecture. They are suitable for experimentation in many areas, such as compiler design, hardware verification, automated VLSI synthesis, systolic processing<sup>7</sup> and general algorithm acceleration. They are particularly suited to various kinds of parallel processing experimentation – pipelining, vector computing and systolic arrangements. Initially, small FPGAs were used as programmable interface controllers between equipment but as their size continued to increase, they quickly outgrew this role. Eventually, groups of FPGAs could be used as a programmable co-processor to accelerate those tasks that were better for novel architectures, rather than those of the von Neumann processor.

<sup>&</sup>lt;sup>6</sup> Data from Carnegie-Mellon University,

http://www.cs.cmu.edu/afs/cs.cmu.edu/academic/class/15828s98/lectures/0112/index.htm.

<sup>&</sup>lt;sup>7</sup> A type of computation which utilises a number of processors in an array. Each element takes in information from one direction and outputs it in another having applied some algorithm to the data.

### **1.2.6 Programming Reconfigurable ICs**

What follows is a brief discussion of how a typical design flow is utilised in the programming of a FPGA. The Xilinx Foundation series is used as an example system.

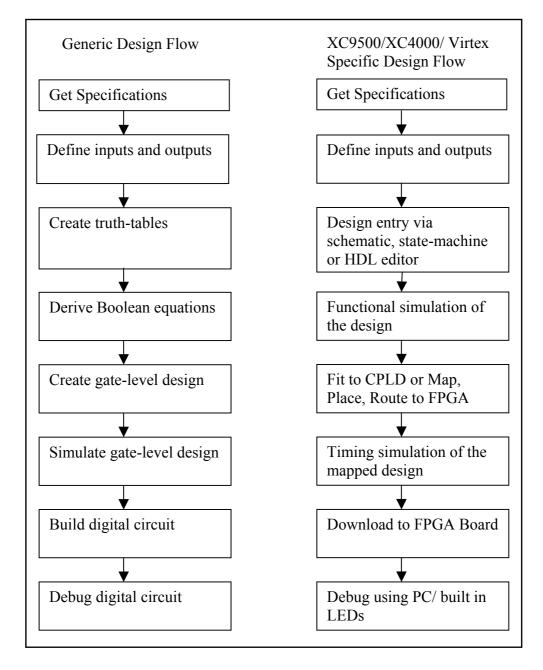

Figure 6. Comparison of generic and FPGA design

The main flow of FPGA design [5] (here using an environment such as Xilinx Foundation 3.1i) to implementation is:

- Design entry: The design can be entered using several different methods Schematic, HDL (ABEL, Verilog, VHDL), Finite State Diagram, CORE generator or LogiBLOX.

- Verification: This stage allows functional and behavioural simulation, for the identification of logic and other errors. Timing at this stage is acquired from standard delay units.

- Synthesis: The design, in a HDL, or as a schematic, is input to the appropriate netlist generator and a netlist (EDIF Netlist, EDN) is output.

- Translate: The input point to this stage is an EDIF (which may be named EDN, or EDIF Netlist) or Xilinx netlist file (XNF), output is a native generic database (NGD) file. In Foundation series software this translation is handled by NGDBuild. This stage merges all of the input netlists, the type of which is determined by a specially invoked program known as the Netlist Launcher. This starts the appropriate netlist reader program. All the various components and references are resolved to form one design. For example, a user constraint file (UCF) may be created that holds timing and location constraints. Through this it is possible to map certain points on the design to certain pins on the chip, as I/O points. The design is then checked using a Logical DRC (Design Rule Check) before finally being written. The NGD output file contains a logical description of the design reduced to Xilinx NGD primitives and a description in terms of the original hierarchy, expressed in the input netlist. This generic file can then be mapped to any desired device family.

- Map: This stage optimises the gates and trims unused logic in the merged NGD netlist. The program in the Foundation series is known as "Map". This step also maps the design's logic resources; logic in the design is mapped to resources in the silicon and a physical design rule check is again performed. The inputs to this stage are the NGD file, the outputs are a native circuit description (NCD) and a physical constraints (PCF) file. The PCF file contains

constraint information usually as a consequence of the conversion of logical constraints from the NGD file which has been input.

- Place and Route: After mapping, the Flow Engine places and routes the design. Foundation series software does this with the Par program. In the Place stage, all logic blocks, including the configurable logic blocks (CLB) and input/output block (IOB) structures, are assigned to specific locations on the die. If timing constraints have been placed on particular logic components, the placer tries to meet those constraints by moving the corresponding logic blocks closer together. As well as timing driven methods, placement can also be governed additionally by cost-based considerations. Cost tables are used which assign weighted values to relevant factors, such as constraints, length of connection and available routing resources. The NCD file and PCF file from the preceding stage are input and a new NCD file is output which contains placement and routing information.

- Configure: The Flow Engine then translates the physical implementation into a configuration file (bit) that is used to program the FPGA. In Foundation software the BitGen executable creates the configuration file. This bitstream can then be downloaded to the chip by several standard programs. The NCD file is input at this point and a final bitstream (.bit) is output. The bit file contains all the configuration information from the NCD file, defining the internal logic and interconnections of the FPGA, plus device-specific information from the other files associated with the target device. The binary data in the bit file can then be downloaded into the FPGA's memory cells.

Several stages can also be added for verification, testing and tracing between each point. There exists ways of retracing steps backward to facilitate both reverse engineering towards another goal (such as conversion to another type of design or target device) and for ways of optimising under constraints, usually by introducing a form of feedback. This allows information on timing to re-enter the design at earlier stages as physical constraints (through PCF files) and therefore lead to improvements.

Most stages also produce reports and log files which trace the progress of a design. Further work can be done on a design if so desired, via editors and debuggers. These can analyse either the design or the actual hardware implementation, allowing visualisation of the implemented design. For example, it is possible to view the design built on the chip and zoom in and view the configuration of the CLBs, IOBs and net distribution. It is also possible to correct problems or alter the layout to a preferred design if part of the silicon is to be used for other reasons (for example, in partial reconfiguration, discussed later). The editor can then re-write a place and routing file, which can be re-loaded into the project for re-synthesis and implementation.

### 1.2.7 Reconfigurability

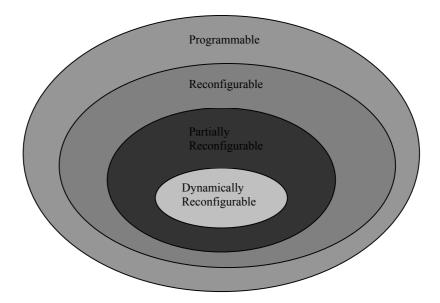

It is possible to view FPGAs in terms of their programmability. All devices of this type are programmable, a subset of this can be re-programmed by terminating the current operation and re-loading a complete device configuration. Another subset of this can be reconfigured partially by stopping operation (making inactive) and loading information only into the area required, without disturbing the rest of the logic circuit. Finally, dynamically reconfigurable FPGAs can be reconfigured while the circuit is still operational and a new design can be implemented in part or fully. It is possible to define the term "compile-time" configurable as referring to reconfigurable FPGAs and dynamically reconfigurable FPGAs as "run-time" reconfigurable.

#### **1.2.8 Partial and Dynamic Reconfiguration**

One of the most tantalising aspects of the FPGA devices is their ability to be reprogrammed while in circuit (this is also known as ISP - in system programmability)<sup>8</sup>. The usual method for the programming of such devices is on power-up but there is an additional capability in the form of causing a reconfiguration to occur at any point by taking a pin, usually called "PROGRAM" to low status. When this is done on a device which is not dynamically reconfigurable, the internal configuration is cleared and re-initialisation occurs. This begins the transfer of the configuration from external memory to the FPGA. On an FPGA which is partially reconfigurable, an inactive chip may have a portion of its area re-loaded.

<sup>&</sup>lt;sup>8</sup> A technical description of active and dynamic reconfiguration is available in the application notes from Xilinx, Dynamic Reconfiguration XAPP093 [53].

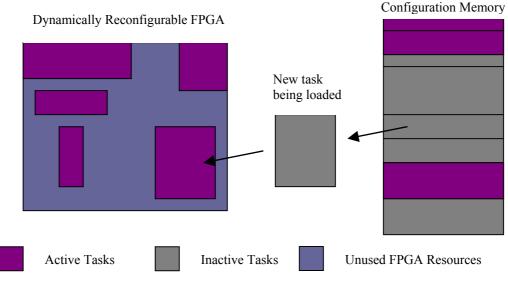

On some devices, such as the Xilinx XC6200 (now only available for research) and the large density Xilinx Virtex family, a dynamic reconfiguration can occur. This allows part of the circuit on chip to be still functioning normally while a reconfiguration of the logic happens elsewhere. The mapping of logic occurs in frames; some data may actually fall upon an active area but only changed patterns will be affected. The main overhead for such dynamic reconfiguration is the time it takes for a transition to take place between the old logic pattern and the new. There are two ways of dealing with this, the first is to use a reconfiguration as mentioned above. The second is to use multiple-context configuration memory maps, which basically "switch-in" another area of the configuration memory to the active context. This context swap can be performed quickly across the entire configurable array, so these devices have the shortest dynamic configuration times. The actual multiple-context configuration memory, however, can occupy large silicon areas.

An FPGA may cause its own reconfiguration by connecting one of its output pins to the program pin. It may also effectively access its own reconfiguration data or have that data mapped into the memory space of an external microprocessor. The external CPU can then alter the data as simply as adjusting variables. Yet another method of controlling reconfiguration is to employ multiple reconfigurable FPGAs, with one or more devices assuming responsibility for loading the configuration data into others.

In devices where the suspension of operation is necessary to implement functional changes, it must be decided whether the algorithm in use is best implemented in a different way if the overhead becomes too great. Any acceleration achieved by using such devices may be lost by this reconfiguration latency. Where different tasks are being performed concurrently, some may complete before others, making optimisation of the complete system difficult. The problem is increased if the device only supports a compile-time static type reconfiguration.

A problem in terms of memory space may occur for large scale devices if only a static reconfiguration is available. Without the ability to partially reconfigure specific areas, IC size bitmaps have to be stored, resulting in enormous areas of memory being required. There may be ways to manipulate the bitmap externally and exploit data

dependencies, by using special procedures to reduce such storage requirements. However, even partial compile-time reconfigurability is probably better than this.

#### 1.2.9 Alternatives to Conventional Systems Architecture

The ability of dynamic reconfiguration to selectively reconfigure active devices leads to the idea that a new system model is possible. By removing the von Neumann processor from the system, its operation can be either absorbed by a large enough FPGA, or replaced by some novel architecture, possibly better suited, or more efficient, to the task in hand. By giving the FPGA access to a RAM block, the system becomes as generic a model for computation as a similar system composed of von Neumann architecture. It would also be possible to include a von Neumann coprocessor where a FPGA may find certain functionality hard to synthesise, for example, in the case of floating point arithmetic. In this instance, the co-processor becomes a arithmetic and logic unit (ALU), any other unrequired functionality can still be absorbed by the FPGA.

The self-reconfiguring system has many advantages to similar microprocessorbased designs. This is in terms of cost and speed (it is not based on the von Neumann interpretive cycle – fetch, decode, execute). It has been found in various practical situations it is simply better to get rid of the processor and rely instead on novel architecture, not based on the interpretive von Neumann model. A benefit of this being that the bottleneck in processing is taken out. This can have cost benefits. Designs can also be realised in what has become conventional, that is, the building block architecture. The array logic used in FPGAs has the speed of hardware with the flexibility of software. The speed factor increase comes from high clock frequencies, inherent parallelism of hardwiring and concurrency that comes from being able to execute multiple tasks on a single array simultaneously.

FPGAs can also be thought of as some extension of the concept of modern day memory. This perspective allows the viewpoint of treating it in a similar way to that of a memory cache in a conventional system. It is possible, in a similar way to a memory cache, to load only those circuits/processes which are currently active. The remainder reside in external RAM and load when required. This technique has been labelled "logic caching" by some.<sup>9</sup> Logic caching can be applied when the FPGA is either self-controlling, or when reconfiguration is controlled externally by the use of a processor.

## 1.2.10 Software Design Tools

There is a current need for better tools that realise the flexibility of reconfigurable devices, for example, there is no way to program such systems in a general purpose manner. Current tools are slow and hardware-oriented. Other software tools are also required which suit reconfigurable systems, such as:

- Simulation Models for dynamic reconfiguration.

- Automatic design partitioning, based on temporal specifications.

- Support for generation of relocatable bitstreams.

- A simulation package for modelling new FPGA architectures.

- Debugging tools [29].

## 1.2.11 Co-Synthesis

One of the main aspects of reconfigurable systems is the allowance of the medium to act in a similar way to memory for the implementation of algorithms. It is through this that makes it possible, in theory, to program it as software but with all the inherent capabilities that accompany a hardwired design. Additionally, there are also other factors which encourage its use, such as cost, flexibility and dynamic reconfiguration.

### 1.2.12 Convergence

The overall theme of this points to a closing of the gap between digital electronic design and the study and practice of computing. The increasing complexity and size of computer systems, in terms of both hardware and software, calls for the development of more comprehensive design tools. Such tools can help view the system as a whole through a unifying model.

It is at the boundaries of systems, in designs and understanding, where most errors are found, usually at sub-system interfaces. This is particularly true of systems which

<sup>&</sup>lt;sup>9</sup> Lysaght 1995 [22].

have hardware and software components, due to the nature of the split in disciplines – allowing for misunderstanding, bad co-ordination and misuse of resources.

Current design methods in both areas are inadequate in working in each other's domains but represent a dichotomy in overall systems design and implementation. When considering the present state-of-the-art, with all its additional functionality inherent, in terms of reconfigurability, concurrency and flexibility, the present design and debugging tools are far from coming close to satisfactory. Hardware description languages are totally inadequate in their description of software; whereas software lacks some of the necessary features but could be adapted to meet the requirements. It is interesting to view the progression of hardware description languages over the last twenty years, which have tended toward becoming programming languages.

It is obvious that the answer to this is the development of a single descriptive language which encompasses the two domains. This may be done in several ways, for example, the language may attempt to describe an algorithm in neutral manner and then be targeted toward either hardware or software. Another way is to embed hardware units, independently developed, within code that is called from the software and executed.

The speed gained from the use of this kind of hardware comes from the inherent parallelism, resulting in extremely fast execution. This parallelism must be described by the programmer for synthesis, which results in a final hardware description. The software itself must describe the appropriate parallelism, or it must be extracted automatically. Given the correct language and tools, it is reasonable to assume that programmers can provide this level of description.

A problem arises in the shape of the two domains, that is; software and digital electronics, being split in such a way. Any programmer, at least in the short term, needs to be able to describe and synthesise hardware and software systems and needs to combine both areas of knowledge, currently belonging to different fields of specialism. Designer-programmers of the future will need to have a greater understanding of how such combined systems operate in terms of parallelism and the temporal behaviour of their designs. This temporal-spatial element in designs is

probably more known to digital engineers than programmers at the moment. It represents not a particularly great challenge but rather a shift in perspective toward training with awareness of spatial and temporal implications in programming.

## **1.3 Current Research and Development in Reconfigurable Systems**

#### 1.3.1 Main areas

There are several main streams of work in this area:

• Hardware and Software Co-Design

This mainly concerns the convergence of the two areas into one; unifying system design. Languages developed to this end tend toward being for specific systems, with some amount of hardware knowledge still being required in their usage [21, 35, 36].

• Fault Tolerance

Through adaptive and reconfigurable technologies it is feasible to suggest that it would be a relatively easy matter to create systems which are adaptable to circumstances and through this, robust in the face of hostile or disruptive environments. This is particularly of interest to military use and currently a heavily funded area by DARPA.

• Rapid Prototyping

The nature of having a "soft" substrate in which to describe hardware components – the so called sea-of-gates allows rapid turnover of new designs.

• Evolvable and Artificial Intelligence

The main ideas here revolve around allowing various weighted stochastic or learning programs generate solutions to problems, particularly based around genetic algorithms (GAs).

Novel Architectures

Experimentation with new kinds of architecture is possible mainly through the ease in which designs can be implemented. Parallel architectures involving pipelines for systolic and vector processing are relatively easy to develop.

#### **1.3.2 Defining the problem tackled here**

A great deal of past work with FPGAs has been held back by tools which rely on older methods of development and those which are based around static deployment of designs within the devices. Recent work has shown the potential available in this technology, particularly in light of the rapid expansion and ubiquity of the internet. This interconnectedness creates the perfect medium for communication with nodes that can use reconfigurable technology to assume whatever function is required.

The work discussed here impacts upon the entire cycle of development, envisaging a design period which extends into run-time. Its main objectives are to explore a fluid, dynamic approach to hardware, utilising knowledge gained in software engineering from various philosophies, such as object-oriented and CSP paradigms. In this way there is a dialogue between the two engineering spheres which inform this project.

A design methodology is required which embraces the mixed module approaches of software and hardware, utilising libraries and tools which express the flexibility of the medium. While there is a movement towards a design methodology similar to that in software engineering, there are many factors which necessarily differ and in some ways, improve, projects developed in this way.

As it is now possible to access state and configuration information at runtime from a device, there are many techniques that can be explored. Objects could be manipulated singularly, for example, for movement and placement. Interrogation of state and configuration is possible and runtime routing would allow additional circuitry to be added at this point.

Built on the above premise, it should be possible to extend the concept of software libraries into runtime, creating a dynamic system, changing content in a similar way to conventional microcomputer memory.

The infrastructure exists for such devices to be configured over network links; it exists in the sense of the appropriate hardware and software servers. The above mobility of entities should not be limited to placement within a device but have network mobility. This allows for remote, dynamic configuration and communication. The project described here therefore aims to promote a fluid, dynamic approach to hardware manipulation in several key areas:

- At design-time, through mixed methods of hardware design input.

- A means of encapsulating hardware entities in the software domain, for transport and software presence/intelligence.

- At delivery time, through mobility of component objects.

- At run-time, through communication and interaction.

While these are the main aspects of the work, the above raises wider implications in several areas, such as language and design synthesis.

# 2. Context

# 2.1 Background

In this section, I will show how research within this area has grown, from initial grappling with definitions, taxonomies and requirements, through to actual systems which deal with the practicalities of implementing such concepts. I will consider these various theories and research, developing from this a set of criteria on which to build the basis of my own approach.

From the early beginnings of development with programmable electronics, the goal has always been to capture some of the flexibility of logic and memory we have in conventional computer software based systems. PLAs, PALs, programmable sequencers and FPGA technology that draw on architecture based on PLDs, are generally still used for logic replacement. FPGAs were originally targeted at traditional "glue logic" applications, replacing other types of PLDs. They were used to perform such functions as address decoding, wait state generation, or bus demultiplexing. The FPGA then evolved into primarily a memory mapped programmable device for implementing custom hardware interfaces. As the size and speed of FPGAs continued to increase, they quickly out-grew this role. It was realised that the devices, or groups of them, could be used as a programmable co-processor, to accelerate tasks better suited to its architecture, than that of the von Neumann processor.

Certain advanced FPGA technology took this a step further by being able to implement complex circuits, logic and memory, in ways that were easily modifiable. The devices soon became viewed as an exciting new medium on which to compile algorithms. They offer an alternative to the traditional von Neumann architecture and are sufficiently complex and cost effective enough to have become the focus for experiments in various areas such as; logic design, timeshared hardware, compiler design, hardware verification, automated VLSI synthesis, systolic processing and general algorithm acceleration. Recent developments allow configuration of these devices to take place while active, modifying only specific areas.

There is still a large gap between the design capabilities of FPGA hardware and the software which supports it. Designs are still, in the main, downloaded as one large design. Even though the general view of the engineer is component or module based, this is relegated to a "static" design-time.

Previous work in this area has realised both the difficulties and possible applications of such devices to be configured on-the-fly [28]. The work has primarily focused on developing a means of mapping designs at run-time, introducing ideas such as logic caching [22] and dynamic synthesis [30].

#### 2.1.1 Taxonomy and Defining the Area

Initial work in this area was carefully explored by Patrick Lysaght and John Dunlop in the paper "Dynamic Reconfiguration of Field Programmable Gate Arrays" [22]. This work outlines the fundamental concepts and definitions for the dynamic and partial reconfiguration of FPGAs. It establishes the consistency of these definitions with terminology used to describe reconfiguration techniques elsewhere in digital electronics<sup>10</sup>.

The paper defines the nomenclature of FPGAs and classification. They may be classified for example, by their configurability. All devices may be, by definition, configurable. A smaller subset may be reconfigured by terminating operation and re-

<sup>&</sup>lt;sup>10</sup> Other notable works included DeHon's Reconfigurable Architectures for General-Purpose Computing, 1996 [9].

loading a complete device configuration (others may have only one download available similar to EPROM style chips). In general, any subset inherits the properties of its parent set, so, any reconfigurable device is programmable but the reverse does not hold.

A device is classed as dynamically reconfigurable if its embedded configuration storage circuitry can be updated selectively, i.e. nominated configuration storage circuits (and the corresponding logic functions and interconnections they control) can be changed without disturbing the operation of the remaining logic. These devices can be therefore configured while still active. This kind of circuitry is referred to as Dynamically Reconfigurable Logic (DRL). Such FPGAs share common features: they are cellular arrays of relatively fine-grained cells, whose configuration is controlled by writing data to static memory locations. The definition of dynamic reconfiguration also implies that a particular FPGA must be capable of partial reconfiguration while active. A device is defined as partially reconfigurable if it is possible to selectively reconfigure it, while the rest of the device remains inactive but retains its configuration information.

Figure 7. Classification of FPGAs according to configurability

It is also noted in this paper that there must be a consistent terminology used. Reconfiguration techniques are widely used in digital electronics for fault and defect tolerance. They are applied in parallel processing, particularly in applications which use processor arrays, such as systolic or wave front processors. Kung [58, 17] introduces the terms "run-time" and "compile-time" to qualify the reconfiguration of VLSI processor arrays. According to these definitions, reconfigurable FPGAs are compile-time reconfigurable and dynamically reconfigurable FPGAs are run-time reconfigurable. It follows from this that the FPGA that is reconfigurable at run-time is also reconfigurable at compile-time.

Other terms have also been defined by numerous authors, including; "staticreconfiguration" to refer to compile-time reconfiguration; "on-line reconfiguration" and "real-time reconfiguration", in place of dynamic reconfiguration.

FPGAs that are not dynamically reconfigurable must be off-line (not active) before a reconfiguration cycle, partial or full, can begin. If such a suspension is required then this limits what can be actually done efficiently on the device. Usage, for example, as a programmable algorithm accelerator, is limited in this case, as even small changes to functionality become critical to its whole operation. Certain algorithms, therefore, become undesirable in this kind of set-up. Such devices also have problems with task organisation, when multiple tasks are being performed concurrently, as certain tasks are likely to complete before others, thus making it difficult to optimise the whole design for maximum speed advantage.

If a reconfigurable FPGA only supports complete reconfiguration the disadvantages multiply. As such devices increase in density and do not include the ability to partially reconfigure, this is likely to become more problematic. There would be, for example, a large overhead resulting from the need to store unique bit maps for every computational permutation. The Xilinx 4008 device (which is relatively small by latest metrics) requires 140,597 bits of programming data for each configuration. The amount of storage required for such a device may be manageable but there are some with hundreds of times the size of such a bit map. Time and storage penalties become inhibiting. The reconfiguration latency may offset any acceleration achieved by the array.

There may be ways to exploit data dependencies within the bit maps by using special procedures, performed externally, to reduce the storage requirements, while at

the same time maintaining transparent access for the FPGA. Partial, compile-time, reconfigurability would be far better than this situation. Compile-time reconfiguration was at one time restricted to the reconfiguration of the entire device, as most devices, such as the Xilinx LCA, were reset prior to reconfiguration. The previous data was therefore lost and partial reconfiguration to implement only a small design change was not possible.

The Lysaght paper also details how such reconfigurations may take place. FPGAs would need, it is posited, a means of being reconfigured if many functional changes are required to its run-time design. For example, a microprocessor could take on the task of loading new designs, or multiple FPGAs could be used with one or more devices assuming responsibility for loading the others. Lysaght also develops the idea of the FPGA being a stand-alone host, replacing the von Neumann computer and where necessary, its functionality. The FPGA in this way becomes an example of a self-controlling, dynamically reconfigurable system. A system is detailed which is set up in a similar way to a conventional computer model i.e. connected to read/write memory. In this way it represents as generic a model of computation as the von Neumann system. The RAM block is critical here, as without it the model is simply that of the FPGA in "master mode". This model can be further altered to include a von Neumann co-processor, which completes tasks not easily implementable or difficult to synthesise efficiently on FPGAs. Such tasks include floating point arithmetic, where the von Neumann co-processor would essentially become an ALU (Arithmetic and Logic Unit); other functions performed by a CPU would be absorbed by the FPGA.

In such scenarios where the FPGA is the centre of a fully programmable system it is a necessity that the device is dynamically reconfigurable. The task in such a case, which controls and initiates the reconfiguration, itself resides on the target, thus making it impossible if the device must be stopped for reconfiguration.

In many applications where there is no need for a microprocessor in the normal sense of the word, self-reconfiguring systems have an immediate cost advantage [39]. The actual way in which FPGAs work also means that the execution of the von Neumann interpretive, fetch, decode and execute does not have to take place, since

the reconfiguration process occurs much less frequently. This represents a significant speed advantage. The actual design of the configuration can also remain in the format popular with digital designers, that is, composed of building blocks.

Lysaght explores how Dynamically Reconfigurable Logic combines properties normally associated with software OR hardware. It offers, for example, the flexibility of programmable solutions and fast operating speeds, which are similar to those of hardware systems. Density on such devices can now reach over 10 million gates, with clock speeds of above 500MHz. The logic is faster than software (when executed on a microprocessor implementing comparable technology) for many applications. This advantage comes from the high clock frequencies, the inherent parallelism of hardwired solutions and the concurrency offered by executing multiple tasks on a single array simultaneously.

## 2.1.2 Logic Caching

Another area investigated and relevant here is logic caching. FPGAs have in the past been described as "programmable active memories". The operation of a selfcontrolling dynamically reconfigurable system can be seen to be analogous to that of a memory cache in a conventional computer system. When operating as a cache, only those circuits that are currently active are held in the memory. The remainder can reside in external RAM and be loaded as and when required. The operation of the logic cache optimises the ratio of active logic, with respect to silicon area. In other words it is possible to store many more circuits in external memory than could be possibly placed in the FPGA's SRAM at any one time. There is generally a greater amount of resources taken up by an implemented design in an SRAM FPGA than the equivalent anti-fuse based programmable device. This is due to the programmable nature of the resources, rather than the logic and spacing itself.

This logic caching in itself does not imply that the underlying system must be selfcontrolling, it is equally valid to use this particular approach in systems where reconfiguration is controlled by an external device, such as another FPGA, microcontroller or processor.

An interesting example is given in the paper, which utilises logic caching. The example employs dynamically reconfigurable logic to monitor in real-time a 64 kbps serial communications link. The instrument employs a multi-phase algorithm which begins with a parallel search of the incoming data for one of five possible framing structures.

The array is programmed to commence operation at the point when time is equal to zero. This compile time loads in six separate tasks T1-T6 and is usually the longest configuration period. There are five frame sequence detectors, T1-T5 and one further task, T6, which performs partial, run-time reconfiguration of the array, when required. Only one of the five frame sequence detectors can achieve frame synchronisation with any given data stream. Once one of the circuits gains frame lock, the other four become redundant. At this point, T6, activates to perform a partial reconfiguration of the array for phase two of the algorithm, while the frame sequence detector which achieved synchronisation, continues to maintain frame lock. The reconfiguration circuit and the synched task survive through a reconfiguration period, the length of which is proportional to the amount of new circuitry being loaded into the array. It is possible at this stage that extra, functionally-redundant data may be needed to be loaded on to the array to make redundant cells inert, by re-initialising them to the

default state. Circuits which have been left in a powered up and semi-functional state have the potential to oscillate, cause cross-talk, or consume power.

The new circuits loaded into the array, called T7 and T8, extract a particular channel from the incoming stream and check the channel contents to whether it contains live traffic or control data. If the most significant bit of the channel byte is set, the channel contains control data and additional circuitry (T9, T10, T11) replace T8 (the data or control detection circuitry) to decode the control information. The new tasks take whatever appropriate action is required, such as the activation of local loopback, or comparison of incoming control data to a locally generated reference, such as a CCITT 16 pseudo random binary random sequence. In the event of loss of frame synchronisation, the data test set suspends current activity and the operation reverts to phase one, via a dynamic reconfiguration, controlled by T6.

In this case a self-controlling system would have to be controlled and reconfigured by tasks T2 and T6. After this first configuration, tasks T2, T6, T7 and T8 are resident on the array. A partial reconfiguration then takes place with tasks T9, T10 and T11 substituted for task T8. At any given time, the maximum number of tasks which may be present simultaneously on the array is determined by a potentially complex relationship. This involves such factors as array size, the combined task sizes and any special requirements, such as input/output pin access, that may be needed if certain tasks are to run.

The example given by Lysaght, illustrates many key points about the algorithms needed in dynamically reconfigurable logic devices which use logic caching<sup>11</sup>. Characteristics shown in this case, such as the algorithm being multi-phase and each phase having several component tasks, are representative of the solutions to various problems utilising this approach.

In the first phase each frame synchronisation detector must execute in parallel for maximum speed of operation, until one circuit detects frame lock. When this happens

<sup>&</sup>lt;sup>11</sup> Logic caching is also explored more recently by K.Compton and S. Hauck, Configuration Caching Techniques for FPGA [8].

all other frame synchronisation circuitry is redundant and the next phase must be implemented. This type of search algorithm is ideal for use in hardware multitasking systems such as this. For any data stream, n-1 of the n frame synchronisation circuits and the tasks that are needed in subsequent phases are mutually exclusive to each other, with respect to time.

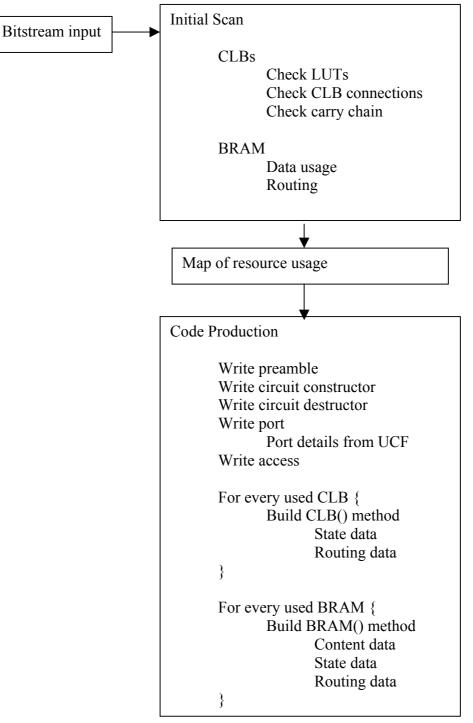

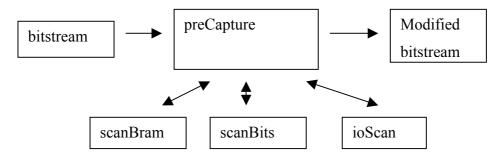

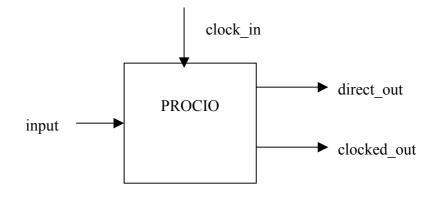

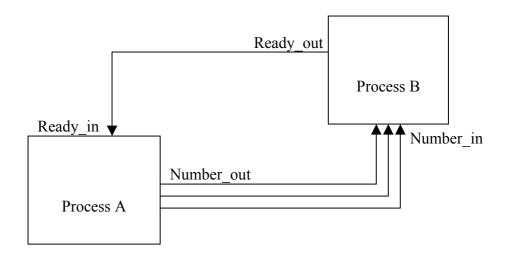

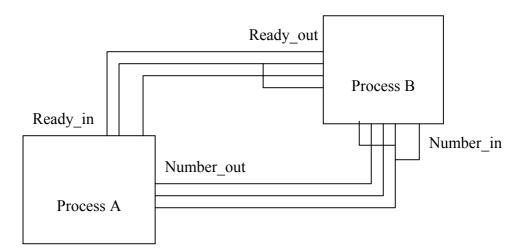

The system detailed above is a real time application that requires several tasks to be executed simultaneously, which is ideally suited to the speed, concurrency and parallelism of a dynamically reconfigurable system. The delay involved in reconfiguring the FPGA is minimal; for example, in this cited case the next stage after frame lock is the user entering information which is several magnitudes greater than the latency involved in the hardware dynamically reconfiguring. The delay involved can be important to take into consideration in most cases. In this case, the application did not need any numerically intensive computations. FPGAs are generally not the best choice for such mathematical calculations as multiplication and square roots, due to the inherent delay characteristics of multi-level logic. Certain applications which are more suited to FPGA synthesis include string matching, error coding and decoding, bit level signal processing and bit level systolic algorithms. It can be difficult to match up applications to the available features and capabilities – programmability and exhibiting the multi-phase, multi-tasking characteristics with mutual-exclusion between tasks over time. Complex digital systems exhibit these features more often.