# The C11 and C++11 Concurrency Model

Mark John Batty Wolfson College University of Cambridge

Saturday  $29^{\text{th}}$  November, 2014

This dissertation is submitted for the degree of Doctor of Philosophy

## Declaration

This thesis does not exceed 61,400 words, and prior permission was granted for an extension of 1,400 words.

### Mark John Batty

### The C11 and C++11 Concurrency Model

University of Cambridge Phone: 07962 440124

Computer Laboratory Email: mbatty@cantab.net

William Gates Building Homepage: www.cl.cam.ac.uk/~mjb220

15 JJ Thomson Avenue Cambridge CB3 0FD, UK

#### Abstract

Relaxed-memory concurrency is now mainstream in both hardware and programming languages, but there is little support for the programmer of such systems. In this highly non-deterministic setting, ingrained assumptions like causality or the global view of memory do not hold. It is dangerous to use intuition, specifications are universally unreliable, and testing outcomes are dependent on hardware that is getting more permissive of odd behaviour with each generation. Relaxed-memory concurrency introduces complications that pervade the whole system, from processors, to compilers, programming languages and software.

There has been an effort to tame some of the mystery of relaxed-memory systems by applying a range of techniques, from exhaustive testing to mechanised formal specification. These techniques have established mathematical models of hardware architectures like x86, Power and ARM, and programming languages like Java. Formal models of these systems are superior to prose specifications: they are unambiguous, one can prove properties about them, and they can be executed, permitting one to test the model directly. The clarity of these formal models enables precise critical discussion, and has led to the discovery of bugs in processors and, in the case of Java, x86 and Power, in the specifications themselves.

In 2011, the C and C++ languages introduced relaxed-memory concurrency to the language specification. This was the culmination of a six-year process on which I had a significant impact. This thesis details my work in mathematically formalising, refining and validating the 2011 C and C++ concurrency design. It provides a mechanised formal model of C and C++ concurrency, refinements to the design that removed major errors from the specification before ratification, a proof in HOL4 (for a restricted set of programs) that the model supports a simpler interface for regular programmers, and, in collaboration with others, an online tool for testing intuitions about the model, proofs that the language is efficiently implementable above the relaxed x86 and Power architectures, a concurrent reasoning principle for proving specifications of libraries correct, and an in-depth analysis of problems that remain in the design.

# Contents

| 1 | Intr | oducti                                               | ion                                                                                                       | 13                         |

|---|------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|

|   | 1.1  | Focus                                                | of this thesis                                                                                            | 19                         |

|   | 1.2  | Contri                                               | ibutions                                                                                                  | 19                         |

|   | 1.3  | Relate                                               | ed work                                                                                                   | 21                         |

| 2 | Bac  | kgroui                                               | $\operatorname{ad}$                                                                                       | 25                         |

|   | 2.1  | Seque                                                | ntial consistency                                                                                         | 25                         |

|   | 2.2  | x86 ar                                               | nd Dekker's algorithm                                                                                     | 27                         |

|   | 2.3  | Even 1                                               | more relaxed: Power and ARM                                                                               | 30                         |

|   | 2.4  | Comp                                                 | iler optimisations                                                                                        | 38                         |

|   | 2.5  | The C                                                | S++11 memory model design                                                                                 | 39                         |

|   |      | 2.5.1                                                | Compiler mappings                                                                                         | 40                         |

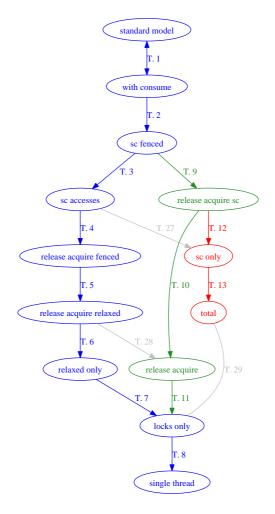

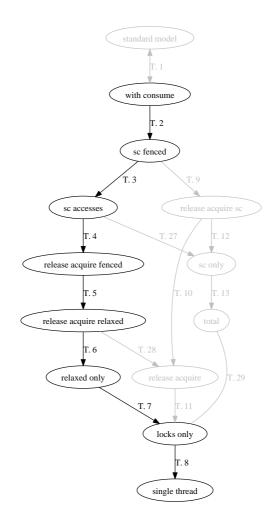

|   |      | 2.5.2                                                | Top-level structure of the memory model                                                                   | 41                         |

|   |      | 2.5.3                                                | Supported programming idioms                                                                              | 42                         |

|   |      | 2.5.4                                                | Standard development process                                                                              | 46                         |

| 3 | The  | forma                                                | al C/C++ memory model                                                                                     | <b>4</b> 9                 |

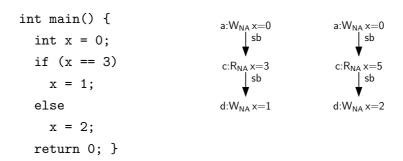

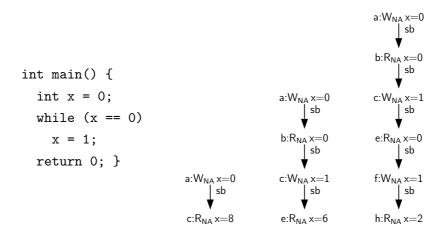

|   | 3.1  | Top-le                                               | evel structure by example: single-threaded programs                                                       | 50                         |

|   |      | 3.1.1                                                | The execution witness, calculated relations and candidate executions                                      | 54                         |

|   |      | 3.1.2                                                | The consistency predicate                                                                                 | 57                         |

|   |      | 3.1.3                                                | Undefined behaviour                                                                                       | 61                         |

|   |      | 3.1.4                                                | Model condition                                                                                           | 63                         |

|   |      | 3.1.5                                                | Management and the level industrial                                                                       | 63                         |

|   |      | 0.1.0                                                | Memory model and top-level judgement                                                                      | Oc                         |

|   | 3.2  |                                                      | threaded programs with locks                                                                              |                            |

|   | 3.2  |                                                      |                                                                                                           | 65                         |

|   | 3.2  | Multi-                                               | threaded programs with locks                                                                              | 65<br>65                   |

|   | 3.2  | Multi-<br>3.2.1                                      | Threaded programs with locks                                                                              | 65<br>65                   |

|   | 3.2  | Multi-<br>3.2.1<br>3.2.2<br>3.2.3                    | Threaded programs with locks  Thread creation syntax  Data races and mutexes  Mutexes in the formal model | 65<br>65<br>66             |

|   |      | Multi-<br>3.2.1<br>3.2.2<br>3.2.3                    | Thread creation syntax                                                                                    | 65<br>65<br>66<br>69       |

|   |      | Multi-<br>3.2.1<br>3.2.2<br>3.2.3<br>Relaxe<br>3.3.1 | Thread creation syntax                                                                                    | 65<br>65<br>66<br>69<br>71 |

|   |      | 3.5.1 Release sequences                                         | 89  |

|---|------|-----------------------------------------------------------------|-----|

|   | 3.6  | Programs with release-acquire fences                            | 93  |

|   | 3.7  | Programs with SC atomics                                        | 98  |

|   |      | 3.7.1 Examining the behaviour of the SC atomics                 | 100 |

|   | 3.8  | Programs with SC fences                                         | 103 |

|   | 3.9  | Programs with consume atomics                                   | 108 |

|   | 3.10 | C/C++11 standard model                                          | 112 |

| 4 | Exp  | lore the memory model with CPPMEM                               | 117 |

|   | 4.1  | Architecture                                                    | 118 |

|   | 4.2  | Interface                                                       | 119 |

| 5 | Des  | ign alterations and critique                                    | 121 |

|   | 5.1  | Acyclicity of happens-before                                    |     |

|   | 5.2  | Coherence axioms                                                | 123 |

|   | 5.3  | Visible sequences of side effects are redundant                 | 126 |

|   | 5.4  | Erroneous claim of sequential consistency                       | 126 |

|   | 5.5  | Missing SC-fence restrictions                                   | 129 |

|   | 5.6  | Undefined loops                                                 | 130 |

|   | 5.7  | Release writes are weaker than they might be                    | 131 |

|   | 5.8  | Carries-a-dependency-to may be too strong                       | 132 |

|   | 5.9  | The use of consume with release fences                          | 133 |

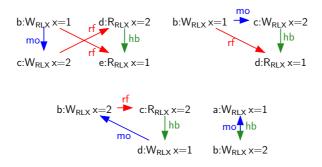

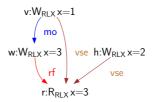

|   | 5.10 | Thin-air values: an outstanding language design problem         | 133 |

|   |      | 5.10.1 Thin-air values, informally                              | 134 |

|   |      | 5.10.2 Possible solutions                                       | 140 |

|   |      | 5.10.3 Java encountered similar problems                        | 142 |

|   |      | 5.10.4 The standard's thin-air restriction is broken            | 144 |

| 6 | Mod  | del meta-theory                                                 | 149 |

|   | 6.1  | Defining the equivalence of models                              | 151 |

|   | 6.2  | Visible sequences of side effects are redundant in the standard | 153 |

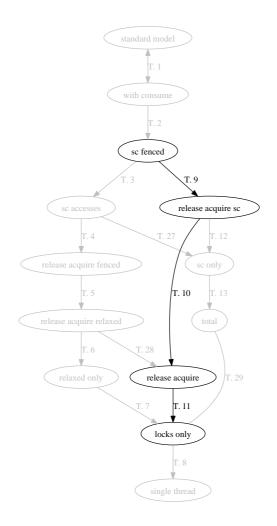

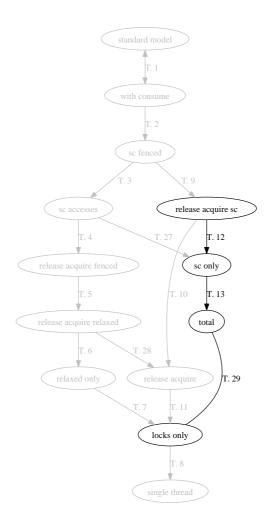

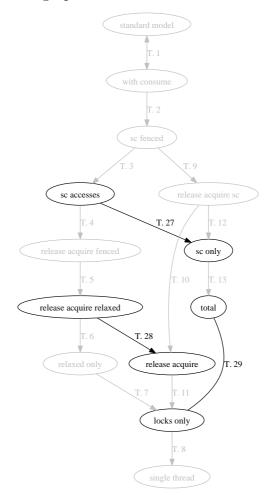

|   | 6.3  | Avoid advanced features for a simpler model                     | 156 |

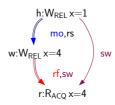

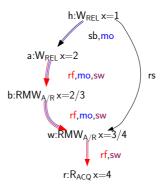

|   | 6.4  | Synchronisation without release sequences                       | 164 |

|   | 6.5  | SC behaviour in the C/C++11 memory model                        | 171 |

|   | 6.6  | Linking the three strands of equivalence                        | 195 |

| 7 | Con  | npilation strategies                                            | 199 |

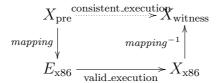

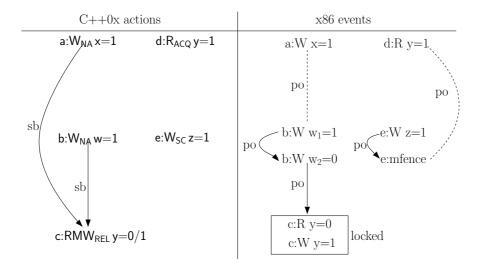

|   | 7.1  | x86 mapping correctness                                         |     |

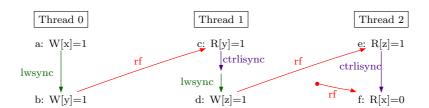

|   | 7.2  | Power mapping correctness                                       | 203 |

|   |      | 7.2.1 Informal correctness of the mapping                       |     |

|   |      | 7.2.2 Overview of the formal proof                              | 207 |

| 8 | Lib   | rary abstraction                                                         | 213        |

|---|-------|--------------------------------------------------------------------------|------------|

|   | 8.1   | A motivating example — the Treiber stack                                 | 214        |

|   | 8.2   | Defining library abstraction                                             | 217        |

|   |       | 8.2.1 Motivating the definition of a history                             | 217        |

|   |       | 8.2.2 The most general client                                            | 219        |

|   |       | 8.2.3 The abstraction relation                                           | 221        |

|   |       | 8.2.4 The abstraction theorem                                            | 221        |

|   | 8.3   | Abstraction in the Treiber stack                                         | 223        |

|   | 8.4   | Soundness of the abstraction relation                                    | 225        |

|   |       | 8.4.1 Necessary definitions                                              | 226        |

|   |       | 8.4.2 Decomposition and composition                                      | 226        |

|   |       | 8.4.3 Proof of soundness of the abstraction relation: Theorem $21 \dots$ | 228        |

| 9 | Cor   | nclusion                                                                 | 231        |

|   | 9.1   | Future work                                                              | 233        |

| • | (D)   |                                                                          | 007        |

| A |       | ${ m e \ C++11 \ standard: \ side-by-side \ model \ comparison}$         | 237<br>237 |

|   | 1 (1) | 1.3 Terms and definitions                                                |            |

|   |       | 1.7 The C++ memory model                                                 |            |

|   |       | 1.8 The C++ object model                                                 |            |

|   |       | 1.9 Program execution                                                    |            |

|   |       | 1.10 Multi-threaded executions and data races                            |            |

|   | 17 I  | Library introduction                                                     |            |

|   |       | 17.6 Library-wide requirements                                           |            |

|   | 29 A  | Atomic operations library                                                |            |

|   |       | 29.1 General                                                             | 268        |

|   |       | 29.2 Header <atomic> synopsis</atomic>                                   |            |

|   |       | 29.3 Order and consistency                                               |            |

|   |       | 29.4 Lock-free property                                                  |            |

|   |       | 29.5 Atomic types                                                        |            |

|   |       | 29.6 Operations on atomic types                                          |            |

|   |       | 29.7 Flag type and operations                                            |            |

|   |       | 29.8 Fences                                                              | 288        |

|   | 30    | Thread support library                                                   |            |

|   |       | 30.1 General                                                             |            |

|   |       | 30.2 Requirements                                                        | 292        |

|   |       | 30.3 Threads                                                             |            |

|   |       | 30.4 Mutual exclusion                                                    |            |

| В | The   | e C++11 standard: side-by-side comparison, following the model           | 305        |

|              | B.1 | The pr | re-execution type                | 305 |

|--------------|-----|--------|----------------------------------|-----|

|              |     | B.1.1  | The action type                  | 306 |

|              |     | B.1.2  | Well-formed actions              | 313 |

|              |     | B.1.3  | Sequenced before                 | 316 |

|              |     | B.1.4  | Additional synchronises with     | 317 |

|              |     | B.1.5  | Data dependence                  | 319 |

|              |     | B.1.6  | Well-formed threads              | 320 |

|              | B.2 | Execu  | tion witness                     | 320 |

|              |     | B.2.1  | Reads-from                       | 321 |

|              |     | B.2.2  | Modification order               | 322 |

|              |     | B.2.3  | Lock order                       | 323 |

|              |     | B.2.4  | SC order                         | 324 |

|              | B.3 | Calcul | ated relations                   | 325 |

|              |     | B.3.1  | Release sequence                 | 325 |

|              |     | B.3.2  | Hypothetical release sequence    | 326 |

|              |     | B.3.3  | Synchronises with                | 327 |

|              |     | B.3.4  | Carries a dependency to          | 333 |

|              |     | B.3.5  | Dependency ordered before        | 334 |

|              |     | B.3.6  | Inter-thread happens before      | 334 |

|              |     | B.3.7  | Happens-before                   | 336 |

|              |     | B.3.8  | Visible side-effects             | 336 |

|              |     | B.3.9  | Visible sequence of side effects | 338 |

|              |     | B.3.10 | Summary of calculated relations  | 339 |

|              | B.4 | The co | onsistency predicate             | 339 |

|              |     | B.4.1  | Coherence                        | 340 |

|              |     | B.4.2  | SC fences                        | 342 |

|              |     | B.4.3  | SC reads                         | 345 |

|              |     | B.4.4  | Consistent locks                 | 346 |

|              |     | B.4.5  | Read determinacy                 | 347 |

|              |     | B.4.6  | The full consistency predicate   | 348 |

|              | B.5 | Undefi | ned behaviour                    |     |

|              |     | B.5.1  | Unsequenced races                | 349 |

|              |     | B.5.2  | Data races                       | 350 |

|              |     | B.5.3  | Indeterminate read               | 352 |

|              |     | B.5.4  | Bad mutex use                    | 352 |

|              |     | B.5.5  | Undefined Behaviour              | 354 |

|              | B.6 | The m  | nemory model                     | 354 |

|              | B.7 | Top-le | vel judgement                    | 354 |

| $\mathbf{C}$ | Lem | n mode | els :                            | 357 |

| Index   | $oldsymbol{4}$                                           | 11          |

|---------|----------------------------------------------------------|-------------|

| Bibliog | raphy 4                                                  | 01          |

| C.19    | Theorems                                                 | 396         |

| C.18    | Total memory model                                       | \$93        |

| C.17    | SC memory model                                          | 392         |

| C.16    | Release-acquire-SC memory model                          | 391         |

| C.15    | Standard memory model                                    | <b>3</b> 90 |

| C.14    | With-consume memory model                                | 888         |

| C.13    | SC-fenced memory model                                   | 85          |

| C.12    | SC-accesses memory model                                 | 84          |

| C.11    | Release-acquire-fenced memory model                      | 82          |

| C.10    | Release-acquire-relaxed memory model                     | 80          |

| C.9     | Release-acquire memory model                             | 378         |

| C.8     | Relaxed-only memory model                                | 376         |

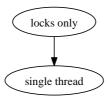

| C.7     | Locks-only memory model                                  | 373         |

| C.6     | Single-thread memory model                               | 370         |

| C.5     | Assumptions on the thread-local semantics for Theorem 13 | 368         |

| C.4     | Well-formed threads                                      | 366         |

| C.3     | Projection functions                                     | 362         |

| C.2     | Types                                                    | 357         |

| C.1     | Auxiliary definitions                                    | 357         |

# Chapter 1

## Introduction

The advent of pervasive concurrency has caused fundamental design changes throughout computer systems. In a bid to offer faster and faster machines, designers had been producing hardware with ever higher clock frequencies, leading to extreme levels of power dissipation. This approach began to give diminishing returns, and in order to avoid physical limitations while maintaining the rate of increase in performance, processor vendors embraced multi-core designs. Multi-core machines contain several distinct processors that work in concert to complete a task. The individual processors can operate at lower frequencies, while collectively possessing computing power that matches or exceeds their single core counterparts. Unfortunately, multi-core processor performance is sensitive to the sort of work they are given: large numbers of wholly independent tasks are ideal, whereas monolithic tasks that cannot be split up are pathological. Most tasks require some communication between cores, and the cost of this communication limits performance on multi-core systems.

Communication between cores in mainstream multi-core machines is enabled by a shared memory. To send information from one core to another, one core writes to memory and the other reads from memory. Unfortunately, memory is extremely slow when compared with computation. Processor designers go to great lengths to reduce the latency of memory by introducing caches and buffers in the memory system. In the design of such a memory, there is a fundamental choice: one can design intricate protocols that hide the details, preserving the illusion of a simple memory interface while introducing communication delay, or one can allow memory accesses to appear to happen out of order, betraying some of the internal workings of the machine. Mainstream processor vendors all opt for the latter: ARM, IBM's Power, SPARC-TSO, and Intel's x86 and Itanium architectures allow the programmer to see strange behaviour at the interface to memory in order to allow agressive optimisation in the memory subsystem.

The behaviour of memory is often abstracted from the rest of the computer system, and is defined by a *memory model* — a description of the allowable behaviours of the memory system. A simple memory model might guarantee that all threads' loads and

stores to memory are interleaved, to form a sequence in which they take effect. A memory model that exposes more behaviours than this simple model is said to be *relaxed*.

Programming languages for concurrent systems must also define an interface to memory, and face the same choice of whether to permit relaxed behaviour or not. Relaxed behaviour can be introduced at the language level either by the underlying processor, or by optimisations in the compiler. If the language decides to forbid relaxed behaviour, then the compiler must disable any optimisations that observably reorder memory accesses, and insert instructions to the processor to disable relaxed behaviour on the hardware. There is an important tradeoff here: disabling these optimisations comes at a cost to performance, but allowing relaxed behaviour makes the semantics of programs much more difficult to understand.

This thesis describes my work on the relaxed memory model that was introduced in the 2011 revision of the C++ programming language (C++11), and that was adopted by the 2011 revision of C (C11). I chose to work on these languages for several reasons. C is the de facto systems programming language, and intricate shared-memory algorithms have an important role in systems programming. The specification of the language was written in a style that was amenable to a formal treatment, and there were stated design goals that could be established with proof. The language specifications had not yet been ratified when I started analysing them, so there was the potential for wide impact.

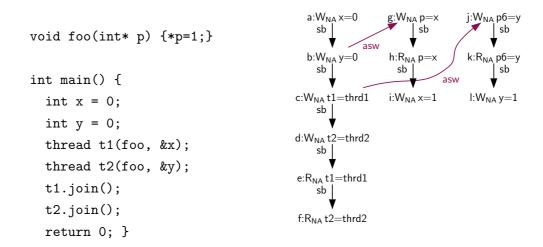

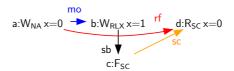

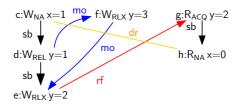

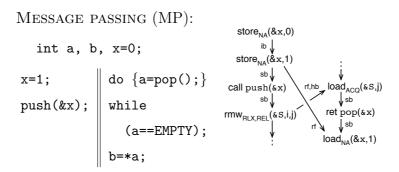

To get a flavour of both the behaviour that relaxed memory models allow, and how one uses the new features of C/C++11, consider the following *message-passing* example (written in C-like pseudocode) where a flag variable is used to signal to another thread that a piece of data is ready to be read:

```

int data = 0;

int flag = 0;

data = 1; || while (flag <> 1){}

flag = 1; || r = data;

```

Here, a parent thread initialises two integer locations in memory, data and flag, each to the value 0, and then creates two threads, separated by a double bar indicating parallel composition: one that writes 1 to data and then to flag, and another that repeatedly reads from flag, waiting for the value 1 before reading data, then storing the result in thread-local variable r, whose initialisation is elided.

One might expect this program to only ever terminate with the final value 1 of variable r: that is the only outcome allowed by a naive interleaving of the accesses on each thread. But an analogous program executed on a Power or ARM processor could, because of optimisations in the memory system, terminate with value 0 stored to r, and to similar effect, a compiler might reorder the writes to data and flag when optimising the left-hand thread. This behaviour breaks our informal specification of this code: the data was not ready to be read when we saw the write of the flag variable. In general, as in this

case, relaxed behaviour can be undesirable: the correctness of the program might depend on its absence.

Hardware architectures like Power and ARM give the programmer barrier instructions that can be inserted to forbid this sort of behaviour, but inserting them degrades performance. In a similar fashion, C/C++11 provides the programmer with the *atomics* library that can be used to forbid the outcome where  $\mathbf{r}$  reads 0, as in the following example:

Here the flag variable is declared as an atomic, and loads and stores of flag use a different syntax that includes a memory-order parameter (release and acquire, above). These new load and store functions perform two tasks: depending on the chosen memory order, they forbid some compiler optimisations, and they force the insertion of barrier instructions on some target architectures. Together, the choice of atomic accesses and memory-order parameters above forbids the outcome where  $\mathbf{r}$  reads 0.

The 2011 C and C++ standard documents describe a memory model that defines the behaviour of these atomic accesses. The 2014 revision of C++ leaves this model unchanged, with only minor updates. Prior to 2011, the semantics of concurrent memory accesses in both languages had been specified by the Posix thread library [53], but in 2005 Hans Boehm noted [36] that when concurrency is described by a library, separate from the language specification, then there is a circularity between the two in the definition of the semantics. Following this observation, there was an effort to define the concurrency behaviour of C++ within the language specification. This thesis focuses on the relaxed memory model that was developed over the subsequent 6 years.

Programming language memory models Language designers have great freedom in their choice of memory model, and here we explore that design space. First we motivate the need for memory models, and then discuss minimal features that are necessary for concurrent programming. We go on to discuss the merits of models that provide strong ordering guarantees, and contrast them with the advantages of more relaxed models. Finally we discuss models that impose requirements on the programmer that are intended to provide some advantages of both strong and relaxed models.

A programming language might abstain from defining a memory model, and leave the language subject to the relaxed behaviour introduced by the target hardware and the optimisations of a particular compiler, but this damages program portability: different choices of compiler optimisations or a different series of processor within a common architecture may admit different behaviours. To be assured of the correctness of their code, a developer would have to test each supported configuration individually. Worse still, relaxed-concurrency bugs can be sensitive to the execution environment and manifest with low probability, so this scheme mandates enormous testing resources. A well-defined memory model provides an abstraction of all of the various platforms that a program might execute above, and constrains their behaviour. It is then the responsibility of compiler writers and processor vendors to ensure that each platform meets the guarantees provided by the memory model. Defining a memory model enables the creation of tools that support portable concurrent programming, and avoids the need for interminable testing resources.

Attiya et al. showed that any concurrent programming language must include a minimal set of features in order to enable the programmer to construct consensus during the execution of their programs [19]; multiple threads must be able to agree on the state of a given piece of data. In a relaxed memory model, this can be an expensive operation: it requires some level of global synchronisation. On the hardware, the operations that provide this feature may be tightly linked to the hardware optimisations that they restrict, but in programming languages, the analogous constructs can be more intuitive. The specification of such features represents one axis in the design space.

The language memory model can provide strong ordering of memory accesses, or it can allow reordering. Strongly ordered memory models like sequential consistency (SC, see §2 for more details), where memory accesses are simply interleaved, have the advantage of usability: programmers need not consider intricate interactions of relaxed concurrent code — the most complex behaviour is simply forbidden. On the other hand, strong models force the compiler to emit code that implements the strong ordering guaranteed by the language. That may restrict the optimisations and force the introduction of explicit synchronisation in the emitted binaries, with a substantial overhead on modern multi-core processors.

At the other end of the spectrum, languages can provide a very relaxed memory model with the possibility of efficient implementation above relaxed processors, but this exposes the programmer to additional complexity. If the guarantees about the ordering of memory are too weak, then it can be impossible to build programs that implement reasonable specifications. Relaxed models can include explicit synchronisation features that allow the programmer to specify stronger ordering in parts of the program. This might take the form of mutexes, fences, barriers, or the memory-order annotations present in the example above. Given a relaxed model with these features, the programmer is burdened with the delicate task of inserting enough explicit synchronisation to ensure correctness, without introducing too much and spoiling performance.

Languages can provide a stronger model while maintaining efficient implementability by requiring a particular programming discipline. If programmers are required to avoid certain patterns, then their absence becomes an invariant for optimisation within the compiler. If a program fails to obey the discipline, then the language provides weaker guarantees about its behaviour. All of these design decisions represent tradeoffs, and there is no universally superior approach; memory models should be designed in sympathy with the expected use of the programming language.

The C/C++ memory model This thesis focuses on the memory model shared by C and C++. Not only are C and C++ extremely well-used languages, but they represent the state of the art in memory-model design for mainstream programming languages.

The C and C++ languages aspire to be portable, usable by regular programmers who require an intuitive setting, and suitable for expert programmers writing high-performance code. For portability, the language defines a memory model, and for performance that model is relaxed.

The model is stratified by the complexity of its features. In its simplest guise, the memory model provides an intuitive setting for those who write single-threaded programs: the order of memory accesses is similar to that provided by previous sequential versions of the language. For programmers who want to write concurrent programs, there is extensive support provided in the concurrency libraries. This ranges from locks and unlocks, to the atomics library, that provides a low-level high-performance interface to memory.

The C/C++11 memory model design was strongly influenced by the work of Adve, Gharachorloo and Hill [12, 10, 11], who proposed a memory model whose programming discipline dictates that programs must annotate memory accesses that might take part in data races: two accesses on different threads that concurrently contend on the same piece of data. Following this work, in 2008 [37], Boehm and Adve described a simplified precursor of the C/C++11 memory-model design, imposing a similar programming discipline: programmers must declare objects that might be accessed in a racy way, these objects must be accessed only through the atomics library, and data races on all other objects must be avoided. If this discipline is violated in any execution of the program, then every execution has undefined behaviour. This is called a "catch-fire semantics" because programs with undefined behaviour are free to do anything — catch fire, order a thousand pizzas, email your resignation, and so on. This design choice carries a heavy cost to the usability of the language. Suppose a programmer identifies buggy behaviour in part of their program, and would like to debug their code. The program may be behaving strangely because of a race in a completely different part of the program, and this race may not even have been executed in the buggy instance. Debugging such a problem could be very difficult indeed. Note that this model of system programming does not match practice, where programmers try to understand racy programs in terms of an assumed model of the system comprising the compiler and the details of the underlying hardware. In this (unsanctioned) model of the system it is possible to debug racy programs by observing their behaviour, unlike in C/C++11.

Following earlier C++ design discussions [38, 35], Boehm and Adve provided a criteria under which programs executed in their relaxed memory model behave according

to sequential consistency [37], and this became a design goal of the C/C++11 memory model: programs that do not have any un-annotated data races, and that avoid using the lowest-level interface to memory, should execute in a sequentially consistent manner. This provides programmers who do not need to use the highest-performance features with an intuitive memory model (for race-free programs). The guarantee went further, stating that races can be calculated in the context of the sequentially-consistent memory model, rather than in the far more complex setting of the relaxed memory model. This is a powerful simplification that allows some programmers to be shielded from the full complexity of the memory model, while experts have access to high-performance features. Although, in early drafts of the C/C++11 standards, this laudable design goal was compromised (details in Chapter 5), the ratified language does provide this guarantee, as we show in Chapter 6.

The atomics library The atomics library provides versions of commonly used primitive data structures, like fixed-width integers, that can be used to write well-defined racy code. Accessor functions are used to read and write atomic variables. The C11 syntax for some of these is given below:

```

atomic_load_explicit(&x,memory_order)

atomic_store_explicit(&x, v, memory_order)

atomic_compare_exchange_weak_explicit(&x, &d, v, memory_order, memory_order)

```

The memory order argument decides how much ordering the access will create in an execution. There are six choices of memory order:

MEMORY\_ORDER\_SEQ\_CST,

MEMORY\_ORDER\_ACQ\_REL,

MEMORY\_ORDER\_ACQUIRE,

MEMORY\_ORDER\_RELEASE,

MEMORY\_ORDER\_CONSUME, and

MEMORY\_ORDER\_RELAXED.

This list is roughly in order, from strong to weak and expensive to cheap: MEM-ORY\_ORDER\_SEQ\_CST can, under certain circumstances, provide sequentially-consistent behaviour with a substantial cost to performance, whereas accesses given MEM-ORY\_ORDER\_RELAXED exhibit many relaxed behaviours, but enable one to write very high-performance code. Typical concurrent programmers should use the former, whose behaviour is relatively straightforward, and expert programmers can use the whole gamut

of memory orders for fine-grained control over the ordering of memory accesses. The C/C++11 memory model allows a superset of the relaxed behaviour allowed by its target architectures. By choosing stronger memory orders, one can forbid this relaxed behaviour.

#### 1.1 Focus of this thesis

The C and C++ memory models are defined by the International Standards Organisation (ISO) in two lengthy standard documents [30, 8]. Prior to my work, there were drafts describing the C/C++11 memory model, but those drafts, despite careful crafting by experts, were not known to describe a usable language memory model. The prose specifications were untestable, and the model was not well understood. It was not formally established whether the design was implementable, programmable, concise, or even internally consistent, nor had the central design tenets, laid out early in the design process [38, 35] and reiterated by Boehm and Adve [37], been established.

In my work, I have sought to understand the C/C++11 memory model in formal terms, to fix parts that were broken, to prove that the design is usable, and, where fixing problems was not yet possible, to highlight outstanding issues. In this thesis I assess the C/C++11 memory model design, presenting a clear and complete picture of a mainstream programming-language relaxed memory model. This effort both improved the C/C++11 definition and can inform the design of future programming-language memory models.

#### 1.2 Contributions

Chapter 3 describes a formal version of the C/C++11 memory model that was developed in close contact with the standardisation committee. Work on this model fed corrections back to the language specification, and as a consequence, it is very closely in tune with the intention of the committee, and the ratified prose specification. The formal model is written in the specification language Lem [85, 90], and is readable, precise and executable (the full definitions are provided in Appendix C). The features of the model are introduced in stages through a series of cut-down models that apply to programs that do not use all of the language features. This chapter also presents a simplified model omits a redundant part of the specification. This work was developed in discussion with Scott Owens, Susmit Sarkar, and Peter Sewell, but I played the leading role. It was published in POPL in 2011 [28].

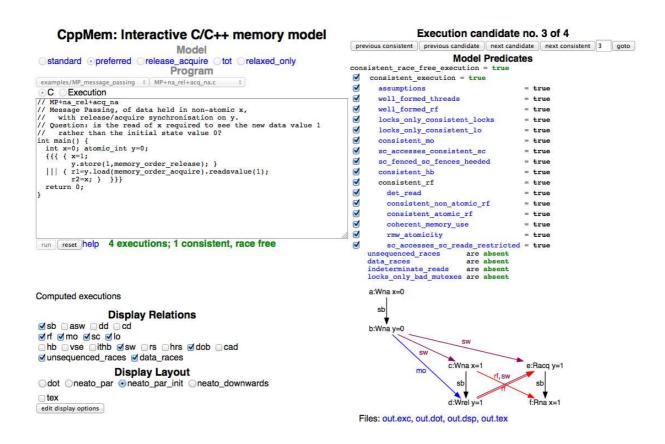

Chapter 4 describes CPPMEM, a tool that takes very small programs and calculates all of the behaviours allowed by the memory model. CPPMEM is joint work with Scott Owens, Jean Pichon, Susmit Sarkar, and Peter Sewell. I contributed to the initial design of the tool, and the tool uses an automatic OCaml translation of my formal memory model produced by Lem. CPPMEM is invaluable for exploring the behaviour of the mem-

ory model. It has been used for communication with the ISO standardisation committee, for teaching the memory model to students, and by ARM, Linux and GCC engineers who wish to understand C/C++11. CPPMEM was described in POPL in 2011 [28], and an alternative implementation of the backend that used the Nitpick counterexample generator [31] was published in PPDP in 2011 [32], in work by Weber and some of the other authors.

Chapter 5 describes problems found with the standard during the process of formalisation, together with solutions that I took to the C and C++ standardisation committees. Many amendments were adopted by both standards in some form. This achievement involved discussing problems and drafting text for amendments with both my academic collaborators and many on the standardisation committee, including: Hans Boehm, Lawrence Crowl, Peter Dimov, Benjamin Kosnik, Nick Maclaren, Paul McKenney, Clark Nelson, Scott Owens, Susmit Sarkar, Peter Sewell, Tjark Weber, Anthony Williams, and Michael Wong. Some of these problems broke the central precepts of the language design. My changes fix these problems and are now part of the ratified standards for C11 and C++11 [30, 8], as well as the specification of the GPU framework, OpenCL 2.0 [86]. This chapter ends by identifying an open problem in the design of relaxed-memory programming languages, called the "thin-air" problem, that limits the compositionality of specifications, and leaves some undesirable executions allowed that will not appear in practice. This leaves the memory model sound, but not as precise as we would like. Many of the comments and criticisms were submitted as working papers and defect reports [29, 20, 75, 73, 111, 27, 76, 77, 74].

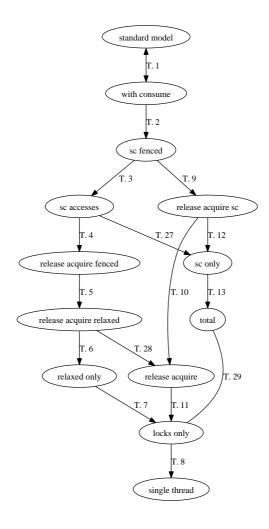

Chapter 6 describes a mechanised HOL4 proof that shows the equivalence of the progressively simpler versions of the C/C++11 memory model, including those presented in Chapter 3, under successively tighter requirements on programs. These results establish that a complicated part of the specification is redundant and can simply be removed, and they culminate in the proof that the specification meets one of its key design goals (albeit for programs without loops or recursion): despite the model's complexity, if a race-free program uses only regular memory accesses, locks and SEQ\_CST-annotated atomic accesses, then it will behave in a sequentially consistent manner. This proof validates that the model is usable by programmers who understand sequential consistency.

Chapter 7 describes work done in collaboration with Jade Alglave, Luc Maranget, Kayvan Memarian, Scott Owens, Susmit Sarkar, Peter Sewell, Tjark Weber and Derek Williams. We took the compilation mappings from C/C++11 to the x86, Power and ARM architectures that had been proposed by the C++11 design group and proved that they do indeed preserve the semantics of the programming-language memory model in execution above those processors. This led to the discovery and resolution of a flaw in one of the mappings. This chapter represents a second form of validation of the formal model: it is implementable above common target architectures. My contribution, which was smaller in this work, involved proving equivalent variants of the C/C++11 memory

model that more closely matched the processors, and discussion of cases in the proof of soundness of the mappings. This work was published in POPL 2011, POPL 2012 and PLDI 2012 [26, 96, 28].

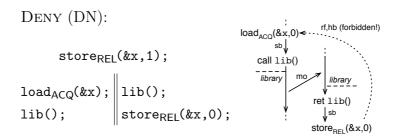

Chapter 8 describes work with Mike Dodds and Alexey Gotsman, developing a compositional reasoning principle for C/C++11. This takes the form of an abstraction relation between a library specification and its implementation. If the specification abstracts the implementation, then we show that the behaviour of a program consisting of arbitrary client code calling the library implementation is a subset of the behaviour of the same client calling the specification. We use this abstraction theorem to prove that an implementation of a concurrent data structure, the Treiber stack, meets its specification. This is another form of validation of the formal model: one can reason about programs with it. My contribution involved writing the implementation and specification of the Treiber Stack and producer-consumer examples, proving that the Treiber Stack specification abstracts its implementation, and contributions to the proof of soundness of the abstraction relation. This work was published in POPL 2013 [25].

Appendix A presents a key piece of evidence that validates the formal model: a side-by-side comparison of the C++11 standard text [30] and the formal memory model presented in Chapter 3, establishing a tight correspondence between the two. Appendix A follows the text of the standard, and is suited to those more familiar with the text. Appendix B presents the same link, following the structure of the model.

Together, this work represents the refinement and validation of a mainstream programming-language memory model. My work establishes that one can write high-performance programs with sound specifications in C/C++11, and that those programs can be correctly compiled to common processor architectures. In the broader context, this work provides a critical analysis of C/C++11 as an example of a relaxed-memory programming language, and identifies design goals for future memory models. The work serves as an example of the benefit of using rigorous semantics in language design and specification.

#### 1.3 Related work

The beginning of this chapter explained that the effort to define a memory model within the C/C++11 specification was motivated by the work of Boehm, who observed that the compiler can interfere with the semantics of relaxed concurrency primitives if they are specified separately from the language [36].

The definition of the C/C++11 memory-model design borrows many concepts from earlier work. The sequential consistency that C/C++11 provides to some programs was first described by Lamport [60]. The combination of relaxed behaviour and explicit programmer-declared synchronisation was a feature of the weak ordering described

by Dubois et al. [48]. C/C++11 coherence matches the coherence property of Censier and Feautrier [42] The compare and swap feature of C/C++11 follows the IBM 370 instruction [44]. C/C++11 provides racy programs with undefined behaviour, a concept borrowed from Adve, Gharachorloo and Hill [12, 10, 11] who defined memory models with stronger guarantees for race-free programs. The C/C++11 memory model builds upon a simple precursor model, defined by Boehm and Adve [37], who expressed the high-level design intent of the memory model (that race-free programs using only the SC atomics should behave in an SC manner), and proved this property of their memory model.

The C/C++11 memory model is expressed in an axiomatic style: the model is made up of a predicate that decides whether a particular whole execution is allowed for a given program, or not. There are several examples of early axiomatic memory models, by Collier [43], by Kohli et al. [13], and by Adve et al. [12, 10]. Contrast this with operational memory models, where the model is described as an abstract machine, with a state made up of buffers and queues. Many formal hardware memory models adopt the operational style [97, 71, 99, 91, 104], because hardware architecture specifications are often described in terms of an abstract machine.

There are many formal memory models of hardware architectures. Sarkar et al. created an operational formalisation of the x86 architecture's memory model [99], following the incomplete and ambiguous published specification documents of the time. This model was superseded by the operational x86-TSO model of Owens et al. [91, 104], which is easy to understand and is validated both by discussion with Intel and by hardware testing. We describe this model in Chapter 2, and refer to it throughout this thesis. In a suggested extension to the architecture, Rajaram et al. propose a hardware-optimised version of C11 read-modify-write operations on x86, including an alternative compilation scheme that preserves the semantics of the language over systems using the optimised variants [93]. For the x86-TSO memory model, Owens provides a stronger alternative to the typical SC-if-data-race-free guarantee, introducing triangular-race-freedom [89].

There are several formal Power memory models to note. Chapter 2 outlines the operational model of Sarkar et al. [97, 71] that was developed together with Williams, a leading processor designer at IBM, and was systematically tested against hardware. This model can claim to match the architectural intent of the vendor. The axiomatic models of Alglave et al. [14] are informed by systematic testing of hardware, with tests generated by the Diy tool [16], executed on current hardware with the Litmus tool [17], and executed according to the model with the Herd tool [18]. This systematic testing led to the discovery of a bug in the Power 5 architecture [16]. Mador-Haim et al. present an axiomatic model [68] that is intended to be abstract and concise, while matching the relatively intricate model of Sarkar et al.

There is an earlier body of work on the Java memory model (JMM), another relaxed-memory language, with a rather different design (discussed in Section 5.10.3). Manson et al. provided a formal description of the official JMM [70]. Cenciarelli et al. provided a

structured operational semantics for the JMM and proved that it is correct with respect to the language specification [41]. Huisman and Petri explore the JMM design and provide a formalisation in Coq [52]. Lochbihler provides a mechanised formal specification of the JMM in Isabelle/HOL, extended to cover a more complete set of features [66, 67]. The Java memory model is intended to admit compiler optimisations, and forbid thin-air behaviour. Ševčík and Aspinall analysed this model and showed that it fails to admit compiler optimisations that are performed by the Hotspot compiler, leaving the model unsound over one of the key compilers for the language [101]. Demange et al. describe an effort to retrofit Java with a buffered memory model similar to that of x86-TSO [46].

There has been some work on compilation of relaxed-memory languages. Ševčík et al. extended Leroy's verified compiler, Compcert [63], to a relaxed-concurrent variant of C with a TSO memory model, in CompcertTSO [102, 103]. Morisset et al. made a theory of sound optimisations over the C/C++11 memory model (as formalised in this thesis), tested compilers and found several bugs in GCC [84].

There have been several formalisations of other parts of C and C++. Norrish provided a mechanised formalisation of C expressions, establishing that a large class of them are deterministic [88]. Ramananandro et al. formalised object layout in C++ and proved several object-layout optimisations correct [94, 95]. Ellison presented a formal thread-local semantics for C [49]. Krebbers formalised C11 dynamic typing restrictions in Coq [59]. Klein et al. provided a formal machine-checked verification of the single-threaded seL4 microkernel [58, 57]. A series of papers by Palmer et al. [92] and Li et al. [64, 65] present a formal specification for a subset of MPI, the high-performance message-passing-concurrency API. None of these addresses shared-memory concurrency.

One line of work has attempted to provide the programmer with a strongly-ordered concurrency model while maintaining the performance of a relaxed model. Sasha and Snir [105] propose recognising dependency cycles in a graph of program segments, and using this analysis to add delay instructions that provide sequential consistency. Gotsman et al. enable a relaxed implementation to hide behind a strongly-ordered interface: they present a variant of linearisability that can be used to show that a library written above the x86-TSO memory model matches a specification in an SC model [50]. To a similar end, Jagadeesan et al. establish an abstraction theorem that allows one to provide sequential specifications to code written above the SC, TSO, PSO and Java memory models [56]. Marino et al. quantify the cost of preserving an SC programming model in the compiler by altering internal LLVM passes to preserve SC, and measuring the slowdown [72]. Alglave et al. provide the Musketeer tool, that performs a scalable static analysis, and automatically inserts fences in order to regain a strong memory model [15].

There are several approaches to the specification and verification of concurrent code in the literature. Schwartz-Narbonne et al. provide a concurrent assertion language for an SC memory model [100]. Burckhardt et al. define linearisability over the TSO memory model [40].

There has been some work on verification for C/C++11. In each piece of work, the presence of thin-air values (discussed in Chapter 5) forces a compromise. Vafeiadis and Narayan presented Relaxed Separation Logic (RSL) for reasoning about C11 programs, and proved it sound in Coq over an augmented C++11 memory model that includes a very strong restriction on thin-air values [110]. Turon et al. present Ghosts, Protocols, and Separation (GPS), a program logic, that can also be used to reason about C11 programs that use release and acquire atomics [109]. Norris and Demsky present CDSchecker, a tool for exhaustive checking of executions of C11 programs [87]. Their tool incrementally executes programs, and will miss executions that feature thin-air behaviour.

There have been several C11 implementations of concurrent data structures. Lê et al. implement an efficient concurrent FIFO queue in C11, test its performance over several hardware architectures, and prove that the code executes as a FIFO queue [61]. With different authors, Lê et al. provide an optimised C11 implementation of Chase and Lev's deque [62].

# Chapter 2

# Background

This chapter includes a brief introduction to three memory models: sequential consistency, the x86 memory model, and the Power memory model (ARM is similar to Power, SPARC-TSO is similar to x86). Sequential consistency is a strong model that is considered to be usable by regular programmers. The x86, Power and ARM architectures (together with Itanium, that we do not consider in detail) represent the most important targets of the C/C++11 language, so the relaxed behaviour that they allow is key to the C/C++11 memory model design. The chapter goes on to introduce the interaction of compiler optimisations with the relaxed memory model, finishing with an overview of the C/C++11 memory model design and the process of its definition.

### 2.1 Sequential consistency

The simplest design choice one might make for a multi-core system would be to imagine that all memory accesses across all cores are interleaved, and belong to a total order. Each memory read would then get the value of the immediately preceding write to the same location in the total order. This memory model is called *sequential consistency* (SC) and was first articulated as such by Lamport [60].

To understand the flavour of sequential consistency, consider the following example (written in C-like pseudocode). A parent thread initialises two integer locations in memory, x and y, each to the value 0 and then creates two threads: one that writes 1 to x and then reads from y, and another that writes 1 to y and then reads from x. Variables r1 and r2 are used only to identify the outcome of the loads, and it is convenient to ignore the memory effects of the writes to each. The example below presents the program using a double bar to indicate the parallel composition of the two child threads, and uses layout to indicate the parent thread above them.

The SC memory model permits any interleaving of the accesses to memory that agrees with the order apparent in the source text of the program, that is: thread-local program order and parent-to-child thread order. The following table lists all possible interleavings of the accesses to memory alongside the resulting outcomes for the values of r1 and r2:

| Interleaving                                | Outcome        |

|---------------------------------------------|----------------|

| x = 0; y = 0; x = 1; y = 1; r1 = y; r2 = x; |                |

| x = 0; y = 0; y = 1; x = 1; r1 = y; r2 = x; | r1 = 1, r2 = 1 |

| x = 0; y = 0; x = 1; y = 1; r2 = x; r1 = y; | 11 - 1, 12 - 1 |

| x = 0; y = 0; y = 1; x = 1; r2 = x; r1 = y; |                |

| x = 0; y = 0; x = 1; r1 = y; y = 1; r2 = x; | r1 = 0, r2 = 1 |

| x = 0; y = 0; y = 1; r2 = x; x = 1; r1 = y; | r1 = 1, r2 = 0 |

Three outcomes are possible for r1 and r2: 1/1, 0/1, and 1/0. The program above is a *litmus test* — a small program, used to test whether a memory model exhibits a particular non-SC memory behaviour.

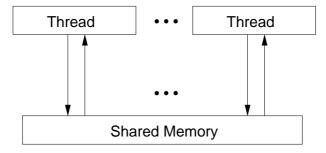

The SC memory model can be thought of as an abstract machine consisting of a single shared memory serving a set of threads, each of which can take steps writing or reading the memory. The following diagram represents this abstract machine:

Any memory model that admits behaviour that is not allowed by the SC model, the outcome 0/0 in the test above for instance, is said to be relaxed. Real processors include intricate optimisations of memory that involve caching and buffering. Maintaining a fully sequentially consistent interface for the programmer would require hiding such optimisations, ultimately reducing performance, so processor designers allow some non-sequentially consistent behaviour to be seen. The outcome 0/0 is allowed for an analogous program on x86, Power and ARM processors, where optimisations in the memory subsystem can delay the write on each thread from reaching the other until the reads have read from the initialisation write. The following sections introduce two common processor architectures: x86 and Power, sketching the details of the memory systems that are made visible to the programmer.

### 2.2 x86 and Dekker's algorithm

The x86 model described here is that of Scott Owens, Susmit Sarkar, and Peter Sewell [91, 104]. The memory model has been validated both by extensive discussion with experts, and by testing on hardware. It covers a useful subset of x86 features, but it ignores non-temporal accesses. This work highlighted deficiencies in the processor architecture documentation, and Intel released further documents that fixed the problems.

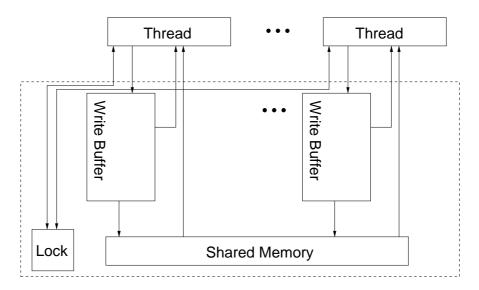

For the sake of performance, the x86 memory model makes some of the details of internal optimisations visible in the form of out-of-order memory accesses. The memory model is best understood as a small change to the SC-abstract machine that was presented in the previous section. Each thread gains a first-in-first-out buffer that temporarily holds writes from that thread before they are flushed to (and become visible in) shared memory. There is also a global lock that can be used to coordinate operations that atomically read and write memory. The abstract machine is as follows:

Execution is still step based: a thread can read or write, as in the SC abstract machine, but now the memory subsystem can take a step too — it can flush a write from the end of one of the threads' write buffers to memory. When a thread writes, the write is added to the thread-local write buffer and leaves the memory unaffected. When a thread reads, it must read the most recent value for the variable present in the thread-local write buffer, if there is one. Only if there is no such write in the buffer does it read from main memory.

Store buffering on x86 makes behaviours observable that would not have been observable on the SC memory model. Recall the example program from the previous section:

On the SC memory model this program had three possible outcomes for the values of r1 and r2: 1/1, 0/1, and 1/0. In x86 a new outcome is possible: 0/0. To understand how, first label the Threads 0, 1 and 2, for the parent, left hand and right hand threads respectively. The label, t:flush;, will be used to describe when the memory system flushes a write from the end of a buffer on thread t. All other accesses to memory will be similarly labeled with the thread that performs them. Now imagine that the x86 abstract machine executes according to the sequence given in the left hand column of the table below. There are columns representing the contents of the write buffers on each thread, and a column representing the contents of memory. Recall that r1 and r2 are just used to identify the values of reads, so their memory behaviour is elided.

| Step      | ,        | Write buffer | •        | Memory   |

|-----------|----------|--------------|----------|----------|

|           | Thread 0 | Thread 1     | Thread 2 |          |

| 0:x = 0;  | x = 0    |              |          |          |

| 0:flush;  |          |              |          | x=0      |

| 0:y = 0;  | y = 0    |              |          | x=0      |

| 0:flush;  |          |              |          | x=0, y=0 |

| 1:x = 1;  |          | x = 1        |          | x=0, y=0 |

| 2:y = 1;  |          | x = 1        | y = 1    | x=0, y=0 |

| 1:r1 = y; |          | x = 1        | y = 1    | x=0, y=0 |

| 2:r2 = x; |          | x = 1        | y = 1    | x=0, y=0 |

| 1:flush;  |          |              | y = 1    | x=1, y=0 |

| 2:flush;  |          |              |          | x=1, y=1 |

When Thread 1 reads from y into r1, there is no write to y in the write buffer of Thread 1, so Thread 1 reads from memory. The write of y on Thread 2 has reached its thread-local write buffer, but has not yet been flushed to memory. Consequently, Thread 1 reads the value 0 from memory. The read of x into r2 takes value 0 symmetrically. This sequence gives rise to the values r1 = 0 and r2 = 0, an outcome that was impossible in the sequentially-consistent memory model. This behaviour, called *store-buffering*, is produced by keeping the write on each thread in its respective write buffer until the reads have completed, and only then flushing the writes to memory. This non-SC behaviour means that x86 is a relaxed memory model.

Note that a read must read its value from the most recent write to the same location in its thread-local write buffer if one exists, so a thread can read its own writes before they become visible to other threads.

The consequences of store-buffering The relaxed behaviour allowed by the x86 architecture can make programs that are correct in the SC memory model incorrect. Take as an example Dekker's algorithm [47], that provides mutual exclusion between threads

over a critical section. Although it is not a well-used mutual-exclusion mechanism in practice, it neatly illustrates the impact of allowing store-buffering relaxed behaviour. Pseudocode for a version of this algorithm is given below:

```

1

int flag0 = 0;

2

int flag1 = 0;

3

int turn = 0;

flag0 = 1;

4

flag1 = 1;

while(flag1 == 1) {

if (turn == 1) {

if (turn == 0) {

5

6

f (turn == 1) {

flag0 = 0;

while (turn == 1);

flag1 = 0;

while (turn == 0);

flag1 = 1;

}

}

7

8

9

}

... critical section ...

10 turn = 1;

11 flag0 = 0;

```

On an SC memory model, this algorithm provides mutual exclusion. To enter the critical section, one thread declares that it will try to enter by writing to its flag variable. It then checks for contention by reading the other thread's flag variable. If there is no contention, then it enters the critical section. Otherwise, the thread engages in a turn-taking protocol, where its flag is written to zero, it waits for its turn, it writes 1 to its flag and then checks the flag on the other thread. If the other thread is contending, it will either pass into the critical section and, on exit, relinquish the turn to the other thread, or be blocked with its flag set to 0, because it is already the other thread's turn.

On the x86 memory model, relaxed behaviour can cause both threads to enter the critical section, breaking mutual exclusion. It is the store-buffering relaxed behaviour that gives rise to this outcome. Recall the shape of the store-buffering litmus test, and compare it to lines 1, 2, 4 and 5 projected out from the Dekker's algorithm example above:

```

int x = 0; int flag0 = 0; int flag1 = 0;  x = 1; \quad y = 1; \quad \text{flag0} = 1; \quad \text{flag1} = 1; \\  r1 = y; \quad r2 = x; \quad \text{while(flag1} == 1)... \quad \text{while(flag0} == 1)...

```

Store-buffering allows both threads to write 1 to their own flag, read the other thread's flag as 0, and then enter the critical section, breaking mutual exclusion.

The x86 architecture provides the facility to flush the thread-local store buffer by adding explicit barriers. In the abstract machine, when a thread encounters an MFENCE barrier, it must wait until its thread-local write buffer has been emptied before continuing with the instructions following the MFENCE. If we augment the store-buffering litmus test with MFENCEs, it becomes:

Now the sequence of steps in the abstract machine that led to the relaxed behaviour is no longer allowed. The writes to  $\mathbf{x}$  and  $\mathbf{y}$  cannot remain in their respective write buffers: before we perform the read on each thread, we will encounter an MFENCE, and must flush the write buffer to memory first, making the relaxed behaviour impossible. Inserting fences into Dekker's algorithm does indeed reestablish mutual exclusion.

Global lock The x86 semantics has a global lock that can be used to atomically read and then write a location in memory. This ability is essential for establishing consensus across multiple threads, and enables us to implement a compare-and-swap primitive in C/C++11. If any processor has acquired the global lock, then only that processor may read from memory until it is released, and on release, that processor's store buffer is flushed.

### 2.3 Even more relaxed: Power and ARM

This section describes the Power memory model of Sarkar et al. [98, 96]. It was developed in close communication with IBM processor architect Williams. The memory model has been validated by extensive discussion with experts, and by testing on hardware. The Power and ARM architectures have similar memory models to one another, and each is more relaxed than that of x86. This section will provide an informal introduction to the Power model, and some of the relaxed behaviour that can be exhibited by it.

We return to the message-passing litmus test that was introduced in Chapter 1, using variables x and y for the data and flag, respectively. This test models a programming idiom where one thread writes some data, here x, then writes to a flag variable, here y. The other thread checks the flag variable, and if the flag has been written, it expects to read the data written by the writing thread.

int x = 0;

int y = 0;

x = 1; | while

$$(y \iff 1)$$

{}

y = 1; | r = x;

Executions of this program might read from y any number of times before seeing the value 1, or they may never see the value 1. We focus on executions where the first read of y reads the value 1, so we simplify the test to remove the loop:

In the sequentially consistent memory model, the behaviour of the program is given by the set of all interleavings of the memory accesses, as presented in the table below:

| Interleaving                               | Outcome        |

|--------------------------------------------|----------------|

| x = 0; y = 0; x = 1; y = 1; r1 = y; r2 = x | r1 = 1, r2 = 1 |

| x = 0; y = 0; x = 1; r1 = y; y = 1; r2 = x |                |

| x = 0; y = 0; r1 = y; x = 1; y = 1; r2 = x | r1 = 0, r2 = 1 |

| x = 0; y = 0; x = 1; r1 = y; r2 = x; y = 1 | 11 - 0, 12 - 1 |

| x = 0; y = 0; r1 = y; x = 1; r2 = x; y = 1 |                |

| x = 0; y = 0; r1 = y; r2 = x; x = 1; y = 1 | r1 = 0, r2 = 0 |

Note that the outcome 1/0 is not allowed under sequential consistency or x86 — the first-in-first-out nature of the write buffers makes it impossible to see the second write without the first already having flushed to memory. On Power, the relaxed behaviour could be introduced by any of the following three architectural optimisations:

- The left hand thread's writes might be committed to memory out of order, by reordering the stores.

- The right hand thread's reads might be performed out of order by some speculation mechanism.

- The memory subsystem might propagate the writes to the other thread out-of-order.

The Power and ARM architectures expose all three sorts of reordering mentioned above, and produce the result 1/0 on the message-passing example.

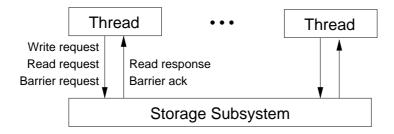

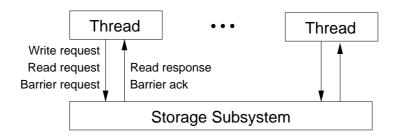

The Power and ARM abstract machine Sarkar et al. define the Power and ARM architecture memory model as an abstract machine. This machine is split between thread-local details such as speculation, and memory-subsystem details such as write propagation. Threads can make write, read and barrier requests, and the memory subsystem can respond with barrier acknowledgements and read responses. Read requests, rather than containing a simple value, are associated with a particular write that is identified by a read-response event. Each read-request from a thread results in an immediate read-response from the storage subsystem.

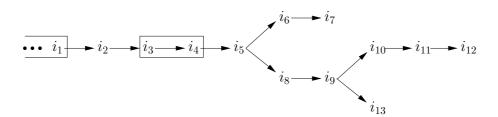

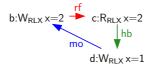

Each thread is represented by an abstract machine that maintains a tree of all possible instructions that the thread might perform, with branches in the tree corresponding to branches in the control flow of the program. Initially, all instructions are marked as in flight. Instructions are then committed one by one, not necessarily in program order. Instructions cannot be committed beyond a branch — the branch itself must be committed first, and the untaken subtree is discarded. Some instructions can be processed before being committed; this allows the speculation of reads (but not writes) beyond uncommitted control flow branches. The following diagram (taken from the tutorial of Maranget et al. [71]) shows an instruction tree, with committed instructions boxed.

In the message-passing example above (without the while loop), there is no branch between the read of y and the read of x, so this mechanism can commit the write of x before the write of y, or the read of x before the read of y, producing the relaxed behaviour in either case.

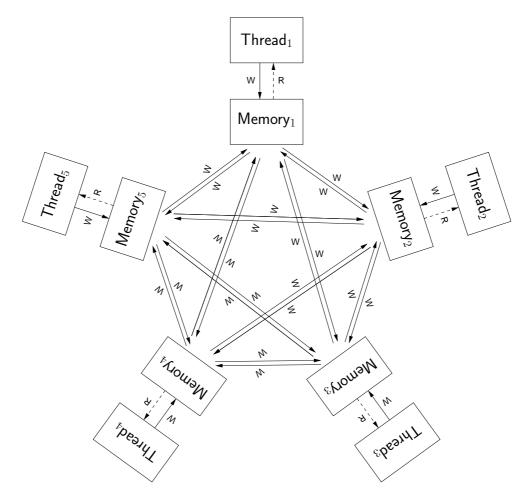

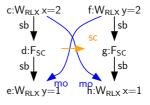

**Propagation lists** For each thread, the abstract machine's storage subsystem maintains a list of the writes and barriers that have been propagated to the thread. Intuitively, the propagation list keeps the set of global events that a thread has observed so far. The storage subsystem can propagate an event from one thread's propagation list to another thread's list at any time, with some caveats. A thread can also commit a write to its own propagation list at any time, again with some caveats. Read requests are satisfied with a write from the thread's propagation list. The diagram below (taken from the tutorial of Maranget et al. [71]) depicts these paths of communication between threads and their propagation lists  $Memory_1$  through  $Memory_5$ :

Propagation order is constrained by barriers and coherence (discussed below), but in the message-passing example there are neither, so the write of  $\mathbf{x}$  can be propagated to the other thread before the write of  $\mathbf{y}$ , permitting the relaxed behaviour.

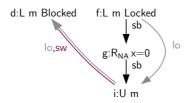

**Coherence** The X86, Power and ARM processors are all *coherent*: the writes to a single location are globally ordered and all reads of the location must see values that are consistent with the order. On x86 writes become visible to all threads when they reach main memory, and the order that writes reach memory orders the writes at each location. So far, there is no analogous order in the Power model.

To ensure coherence, the storage subsystem of the Power abstract machine keeps a coherence-commitment order for each location. This is a partial relation that records the global order in which writes are committed, so that at the end of the execution it will be total. The order is constructed thread-wise, built up from the order in which writes are propagated to each thread.

Read requests can be issued by any thread at any time. Reads are requested and committed separately, and read requests can be invalidated. The propagation list of the issuing thread, and indirectly, the coherence-commitment order, restrict the write that the storage subsystem can return for a given read request. The storage subsystem must return the most recent write of the location in the thread's propagation order, and the

coherence-commitment order restricts which writes can be committed to the propagation list.

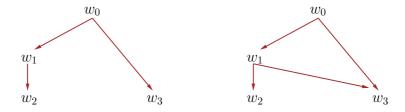

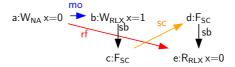

Take for example (from Sarkar et al. in PLDI 2011 [98]) an abstract-machine storage subsystem with the coherence-commitment order as depicted on the left below. Suppose we are interested in one particular thread that is about to perform a read request, and  $w_1$  is the most recent write to the location of the read in the thread's propagation list. The storage subsystem must return the most recent write to the location in the thread's propagation list, so the write returned is decided by which writes may be propagated to the thread before the read request. Consider each of the cases in turn:

- 1. The coherence-earlier write,  $w_0$ , cannot be propagated to the read's thread, so the read cannot see  $w_0$ .

- 2. With no further propagation, the read could see  $w_1$ .

- 3. The reading thread could be propagated  $w_2$ , which would then be seen by the write, leaving coherence order unchanged.

- 4. The reading thread could be propagated  $w_3$ , adding  $w_3$  to the propagation list, and causing it to be seen by the read. This has the effect of adding an edge to the coherence order from  $w_1$  to  $w_3$ , but leaves  $w_2$  and  $w_3$  unordered. The updated coherence graph is on the right above.

Message passing: avoiding relaxed behaviour Now that the Power abstract machine has been introduced, we return to the message-passing example, and the details of the machine that can give rise to the relaxed behaviour:

The three causes of observing the outcome 1/0 in this program were as follows:

- Writes can be committed out of order.

- Writes can be propagated out of order.

- Reads can be requested out of order.

It is easy to imagine programs where the programmer intends to use the messagepassing idiom and the relaxed behaviour would be undesirable, so, much in the same way that x86 provided the MFENCE, Power and ARM provide additional ordering through barriers and dependencies. There are three sorts of dependency from a read, r, to another accesses of memory, a: if the value of r is used to compute the address of the access athen there is an address dependency, if the value of r is written to memory by a there is a data dependency, and if the control flow path that leads to a is selected by the value returned by r then there is a control dependency.

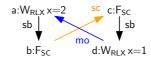

The following program augments the message-passing example, adding an lwsync on the writing thread, and wrapping the second read within an if-statement with an isync barrier, that enforces order of the read requests, so that it is dependent on the value read by the first:

Inserting an lwsync barrier between two writes in the Power architecture (or a dmb for ARM) prevents the writes from being committed or propagated out of order. Similarly, the control dependency added to the reading thread, combined with the isync barrier, prevents the reads from being requested out of order. So with these new additions, the relaxed behaviour is no longer allowed. The Power architecture also provides the sync barrier that is even stronger than the lwsync or a dependency with isync. With liberal use of sync, one can regain sequential consistency.

It is interesting to note that when programming such processors, one can rely on dependencies to provide ordering. It is sufficient to create an artificial dependency that has no real bearing on the execution of the program — the sort of dependency that a compiler would routinely remove. This turns out to be a useful programming idiom, and lies in stark contrast to the treatment of dependencies in programming languages. In the message-passing example above, we can create an artificial address dependency as follows:

This dependency is sufficient to disable the thread-local speculation mechanism, and ensure the relaxed outcome 1/0 is not visible.

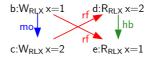

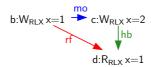

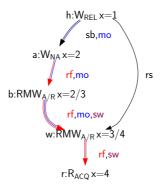

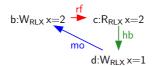

Multi-copy atomicity Some memory models, like x86 and SC, order all of the writes in the system by, for example, maintaining a shared memory as part of the state of the model. Other memory models are weaker and allow different threads to see writes across the system in different orders. Consider the following example, called IRIW+addrs for independent reads of independent writes with address dependencies: